**Preliminary User's Manual**

# μPD1615, μPD16F15, μPD1616

8-bit Single-Chip Microcontroller

Hardware

Document No. U13635EE1V0UM00 Date Published March 1999

© NEC Corporation 1999

FIP is a trademark of NEC Corporation EEPROM and IEBus are trademarks of NEC Corporation. MS-DOS and MS-Windows are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries. PC/AT and PC DOS are trademarks of IBM Corp. IBM-DOS, PC/AT and PC DOS are trademarks of International Business Machines Corporation. HP9000 Series 300, HP9000 Series 700, and HP-UX are trademarks of Hewlett-Packard Company. SPARCstation is a trademark of SPARC International, Inc. Sun OS is a trademark of Sun Microsystems, Inc. Ethernet is a trademark of Xerox Corp. NEWS and NEWS-OS are trademarks of Sony Corporation. OSF/Motif is a trade mark of OpenSoftware Foundation, Inc.. TRON is an abbreviation of The Realtime Operating system Nucleus. ITRON is an abbreviation of Industrial TRON.

The related documents in this publication may include preliminary versions. However, preliminary versions are not marked as such.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features. NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard:Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books.

If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

NF

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 800-366-9782 Fax: 800-729-9288

NEC Electronics (Germany) GmbH Duesseldorf, Germany Tel: 0211-65 03 02

Fax: 0211-65 03 490

#### NEC Electronics (UK) Ltd. Milton Keynes, UK

Tel: 01908-691-133 Fax: 01908-670-290

## NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

NEC Electronics (France) S.A. Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

## NEC Electronics (France) S.A.

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

## NEC Electronics (Germany) GmbH

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 253-8311 Fax: 250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

### NEC do Brasil S.A.

Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

## Introduction

#### Readers

This manual has been prepared for user engineers who want to understand the functions of the  $\mu$ PD1615 subseries and design and develop its application systems and programs.

μPD1615 Subseries: μPD1615, μPD16F15, μPD1616.

#### Purpose

This manual is intended for users to understand the functions described in the Organization below.

### Organization

The µPD1615 subseries manual is separated into two parts: this manual and the instruction edition (common to the 78K/0 series).

- Pin functions

- Internal block functions

- Interrupt

- Other on-chip peripheral functions

- CPU functions

- Instruction set

- Explanation of each instruction

### How to Read This Manual

Before reading this manual, you should have general knowledge of electric and logic circuits and microcontrollers.

- When you want to understand the function in general:

- $\rightarrow$  Read this manual in the order of the contents.

- How to interpret the register format:

- → For the bit number enclosed in square, the bit name is defined as a reserved word in the assembler and the compiler.

- To make sure the details of the registers when you know the register name.

- $\rightarrow$  Refer to **Appendix C.**

## **Chapter Organization**

This manual devides the descriptions for the subseries into different chapters as shown below. Read only the chapters related to the device you use.

|            | Chapter                           | µPD1615 | µPD16F15 | µPD1616 |

|------------|-----------------------------------|---------|----------|---------|

| Chapter 1  | Outline                           | 0       | 0        | 0       |

| Chapter 2  | Pin Function                      | 0       | 0        | 0       |

| Chapter 3  | CPU Architecture                  | 0       | 0        | 0       |

| Chapter 4  | Port Functions                    | 0       | 0        | 0       |

| Chapter 5  | Clock Generator                   | 0       | 0        | 0       |

| Chapter 6  | 16-Bit Timer/Counter              | 0       | 0        | 0       |

| Chapter 7  | 8-Bit Timer/Event Counters 50, 51 | 0       | 0        | 0       |

| Chapter 8  | Watch Timer                       | 0       | 0        | 0       |

| Chapter 9  | Watchdog Timer                    | 0       | 0        | 0       |

| Chapter 10 | Clock Output Control Circuit      | 0       | 0        | 0       |

| Chapter 11 | A/D-Converter                     | 0       | 0        | 0       |

| Chapter 12 | Serial Interface Outline          | 0       | 0        | 0       |

| Chapter 13 | Serial Interface Channel 30       | 0       | 0        | 0       |

| Chapter 14 | Serial Interface UART             | 0       | 0        | 0       |

| Chapter 15 | VAN Controller                    | 0       | 0        | 0       |

| Chapter 16 | LCD Controller/Driver             | 0       | 0        |         |

| Chapter 17 | Sound Generator                   | 0       | 0        | 0       |

| Chapter 18 | Interrupt Functions               | 0       | 0        | 0       |

| Chapter 19 | Standby Function                  | 0       | 0        | 0       |

| Chapter 20 | Reset Function                    | 0       | 0        | 0       |

| Chapter 21 | μPD16F15                          | 0       | 0        | 0       |

| Chapter 22 | Instruction Set                   | 0       | 0        | 0       |

| Appendix A | Development Tools                 | 0       | 0        | 0       |

| Appendix B | Embedded Software                 | 0       | 0        | 0       |

| Appendix C | Register                          | 0       | 0        | 0       |

| Appendix D | Revision History                  | 0       | 0        | 0       |

## **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### • Related documents for µPD1615 subseries

| Document name                                     | Document No. |             |

|---------------------------------------------------|--------------|-------------|

|                                                   | Japanese     | English     |

| µPD1615 Preliminary Product Information           | —            | U13723E     |

| µPD16F15 Preliminary Product Information          | —            | U13606E     |

| µPD1615 Subseries User's Manual                   | —            | This manual |

| 78K/0 Series User's Manual-Instruction            | IEU-849      | IEU-1372    |

| 78K/0 Series Instruction Table                    | U10903J      | —           |

| 78K/0 Series Instruction Set                      | U10904J      | U12326E     |

| µPD1615 Subseries Special Function Register Table | _            | _           |

## • Related documents for development tool (User's Manuals)

|                                          |                                   | Document No. |          |

|------------------------------------------|-----------------------------------|--------------|----------|

| Document r                               | Document name                     |              | English  |

| RA78K Series Assembler Package           | Operation                         | EEU-809      | EEU-1399 |

|                                          | Language                          | EEU-815      | EEU-1404 |

| RA78K Series Structured Assembler Prepro | cessor                            | EEU-817      | EEU-1402 |

| CC78K Series C Compiler                  | Operation                         | EEU-656      | EEU-1280 |

|                                          | Language                          | EEU-655      | EEU-1284 |

| CC78K/0 C Compiler                       | Operation                         | U11517J      | _        |

|                                          | Language                          | U11518J      | _        |

| CC78K/0 C Compiler Application Note      | Programming Note                  | EEA-618      | EEA-1208 |

| CC78K Series Library Source File         |                                   | EEU-777      | —        |

| IE-78001-R-A                             |                                   | U10057J      | U10057E  |

| IE-78K0-NS-P04                           |                                   | —            | U13359E  |

| IE-1615-NS-EM4                           |                                   |              |          |

| IE-78K0-R-EX1                            |                                   | SUD-3677     | SUD-3677 |

| EP-78230GC-12                            | —                                 | TEMPR-2093   | U10181E  |

| SM78K0 System Simulator Windows™ Base    | Reference                         | U10181J      | U10092E  |

| SM78K0 Series System Simulator           | External part user open Interface | U10092J      | —        |

| ID78K0 Integrated Debugger EWS Base      | Reference                         | U11151J      | U11539E  |

| ID78K0 Integrated Debugger PC Base       | Reference                         | U11539J      | U11649E  |

| ID78K0 Integrated Debugger Windows Base  | Guide                             | U11649J      |          |

## • Related documents for embedded software (User's Manual)

| Document name                                                                      |              | Document No. |          |

|------------------------------------------------------------------------------------|--------------|--------------|----------|

|                                                                                    |              | Japanese     | English  |

| 78K/0 Series Real-Time OS                                                          | Basics       | U11537J      | _        |

|                                                                                    | Installation | U11536J      | _        |

|                                                                                    | Technicals   | U11538J      | —        |

| 78K/0 Series OS MX78K0                                                             | Basics       | EEU-5010     | —        |

| Fuzzy Knowledge Data Creation Tool                                                 |              | EEU-829      | EEU1438  |

| 78K/0, 78IK/II, 87AD Series Fuzzy Inference Development Support System-Translator  |              | EEU-862      | EEU-1444 |

| 78K/0 Series Fuzzy Inference Development Suppport System- Fuzzy Inference Module   |              | EEU-858      | EEU-1441 |

| 78K/0 Series Fuzzy Inference Development Suppport System- Fuzzy Inference Debugger |              | EEU-921      | EEU-1458 |

## • Other Documents

|                                                                   | Document No. |          |

|-------------------------------------------------------------------|--------------|----------|

| Document name                                                     | Japanese     | English  |

| IC Package Manual                                                 | C10943X      |          |

| Semiconductor Device Mounting Technology Manual                   | C10535J      | C10535E  |

| Quality Grade on NEC Semiconductor Devices                        | C11531J      | C11531E  |

| Reliability Quality Control on NEC Semiconductor Devices          | C10983J      | C10983E  |

| Electric Static Discharge (ESD) Test                              | MEM-539      | _        |

| Semiconductor Devices Quality Assurance Guide                     | MEI-603      | MEI-1202 |

| Microcontroller Related Product Guide - Third Party Manufacturers | U11416J      | _        |

## Caution: The above documents are subject to change without prior notice. Be sure to use the latest version document when starting design.

## **Table of Contents**

| Chapter 1 Outline |                                                                    | 26 |

|-------------------|--------------------------------------------------------------------|----|

| 1.1               | Features                                                           | 26 |

| 1.2               | 2 Application                                                      | 26 |

| 1.3               | 3 Ordering Information                                             | 26 |

| 1.4               | Pin Configuration (Top View)                                       | 27 |

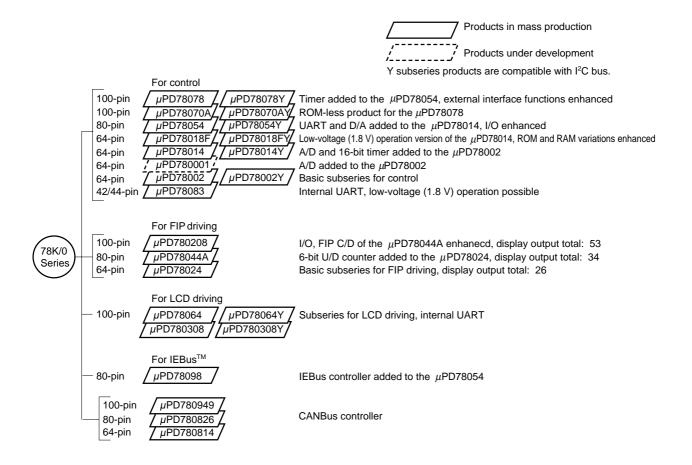

| 1.5               | 5 78K/0 Series Development                                         | 30 |

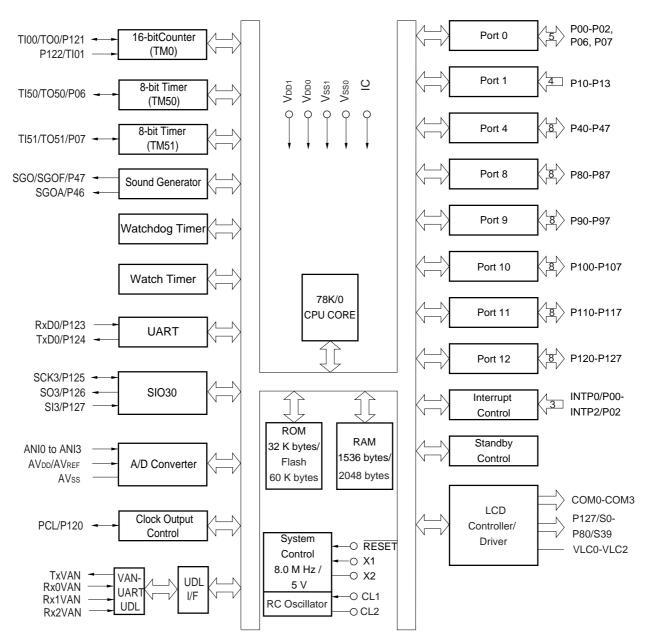

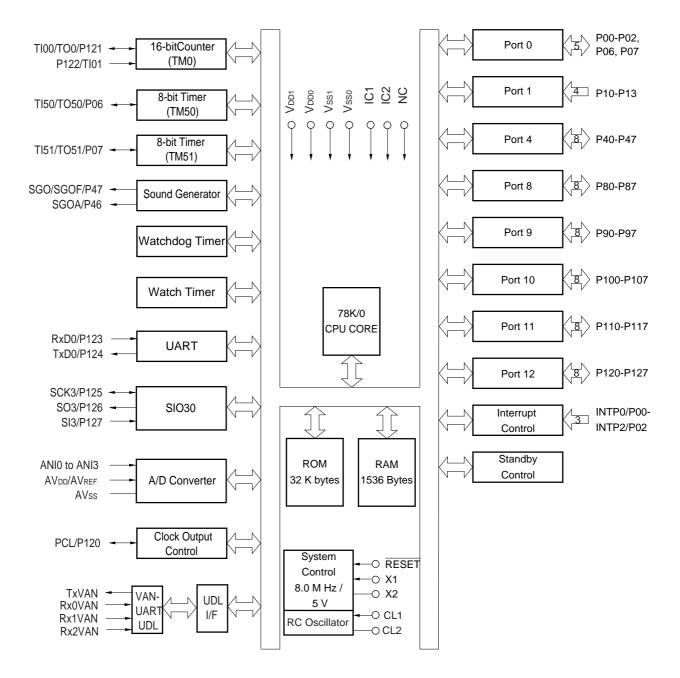

| 1.6               | 6 Block Diagram                                                    | 31 |

| 1.7               | 7 Overview of Functions                                            | 33 |

| 1.8               | 3 Mask Options                                                     |    |

|                   | <ul> <li>Differences between Flash and Mask ROM version</li> </ul> |    |

| Chapter 2 Pin Function                                         | 36   |

|----------------------------------------------------------------|------|

| 2.1 Pin Function List                                          | . 36 |

| 2.2 Non-Port Pins                                              | . 38 |

| 2.3 Description of Pin Functions                               | . 40 |

| 2.3.1 P00 to P02, P06 and P07 (Port 0)                         | . 40 |

| 2.3.2 P10 to P13 (Port 1)                                      | . 40 |

| 2.3.3 P40 to P47 (Port 4)                                      | . 40 |

| 2.3.4 P80 to P87 (Port 8)                                      | . 41 |

| 2.3.5 P90 to P97 (Port 9)                                      | . 41 |

| 2.3.6 P100 to P107 (Port 10)                                   | . 41 |

| 2.3.7 P110 to P117 (Port 11)                                   | . 41 |

| 2.3.8 P120 to P127 (Port 12)                                   | . 42 |

| 2.3.9 COM0 to COM3                                             | . 42 |

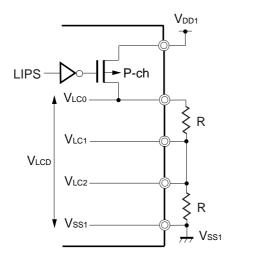

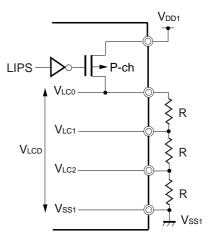

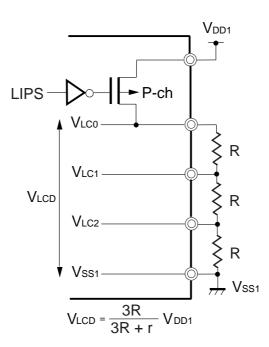

| 2.3.10 VLC0 to VLC2                                            | . 42 |

| 2.3.11 AVDD/AVREF                                              | . 43 |

| 2.3.12 AVSS                                                    | . 43 |

| 2.3.13 RESET                                                   | . 43 |

| 2.3.14 X1 and X2                                               | . 43 |

| 2.3.15 CL1 and CL2                                             | . 43 |

| 2.3.16 VDD0/VDD1                                               | . 43 |

| 2.3.17 VSS0/VSS1                                               | . 43 |

| 2.3.18 VPP (μPD16F15 only)                                     | . 43 |

| 2.4 Pin I/O Circuits and Recommended Connection of Unused Pins | . 44 |

|                                                                |      |

| Chapter 3 CPU Architecture                       | . 51 |

|--------------------------------------------------|------|

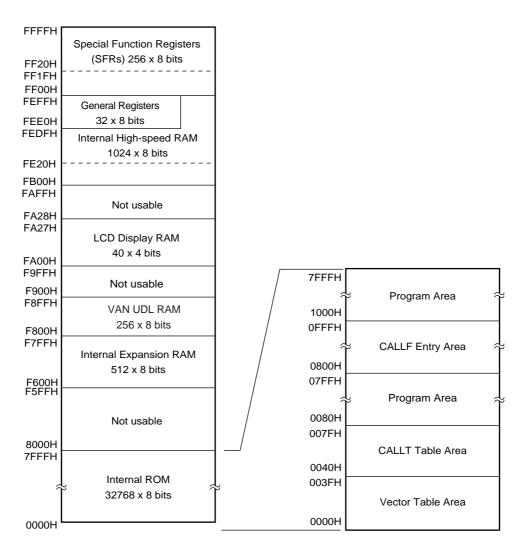

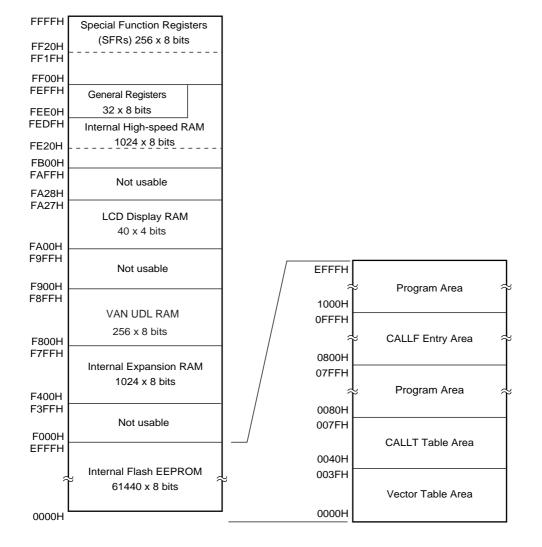

| 3.1 Memory Space                                 | 51   |

| 3.1.1 Internal program memory space              | 53   |

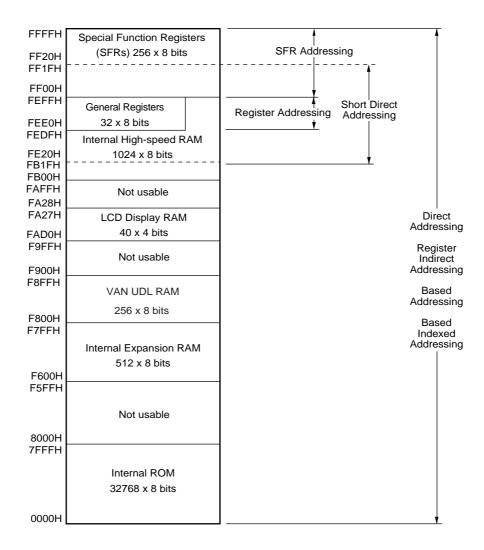

| 3.1.2 Internal data memory space                 | 55   |

| 3.1.3 Special function register (SFR) area       | 55   |

| 3.1.4 Data memory addressing                     | 56   |

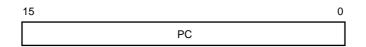

| 3.2 Processor Registers                          | 58   |

| 3.2.1 Control registers                          | 58   |

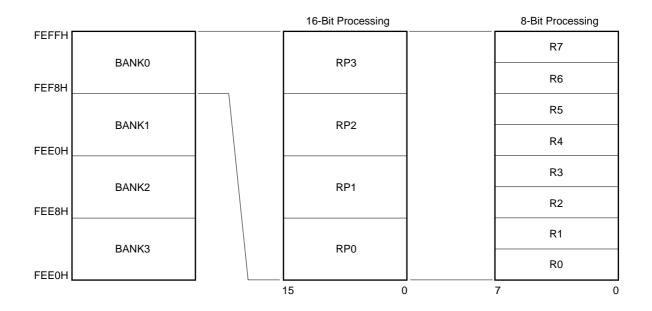

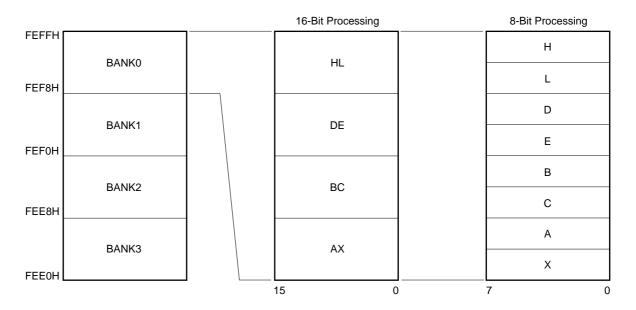

| 3.2.2 General registers                          | 61   |

| 3.2.3 Special function register (SFR)            | 62   |

| 3.3 Instruction Address Addressing               | 65   |

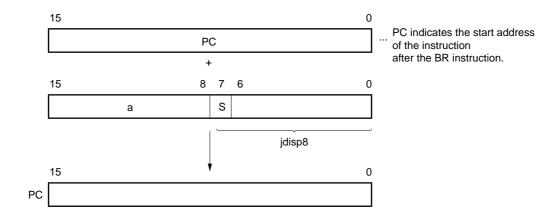

| 3.3.1 Relative addressing                        | 65   |

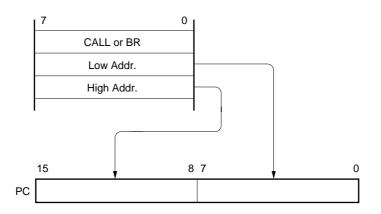

| 3.3.2 Immediate addressing                       | 66   |

| 3.3.3 Table indirect addressing                  | 67   |

| 3.3.4 Register addressing                        | 68   |

| 3.4 Operand Address Addressing                   | 69   |

| 3.4.1 Implied addressing                         | 69   |

| 3.4.2 Register addressing                        | 70   |

| 3.4.3 Direct addressing                          | 71   |

| 3.4.4 Short direct addressing                    | 72   |

| 3.4.5 Special function register (SFR) addressing | 73   |

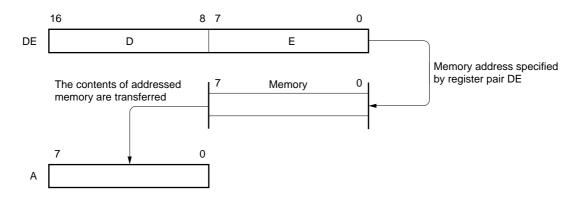

| 3.4.6 Register indirect addressing               | 74   |

| 3.4.7 Based addressing                           | 75   |

| 3.4.8 Based indexed addressing                   | 76   |

| 3.4.9 Stack addressing                           | 76   |

| Chapter 4 Port Functions                         | . 78 |

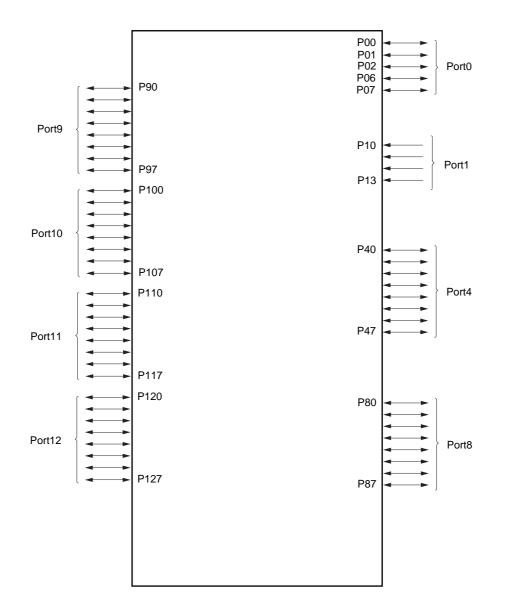

| 4.1 Port Functions                               | 78   |

| 4.2 Port Configuration                           | 81   |

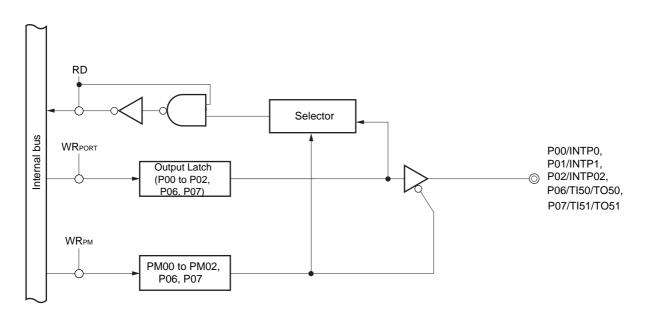

| 4.2.1 Port 0                                     | 81   |

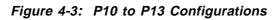

| 4.2.2 Port 1                                     | 83   |

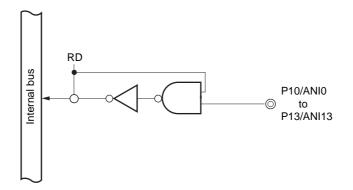

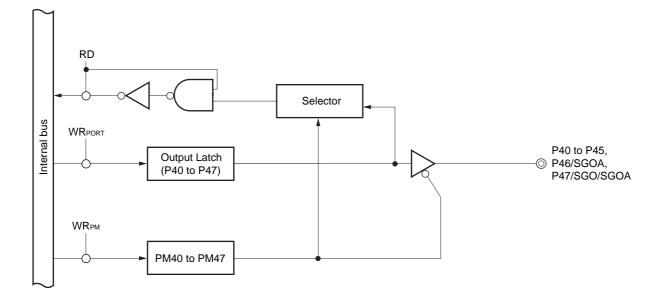

| 4.2.3 Port 4                                     | 84   |

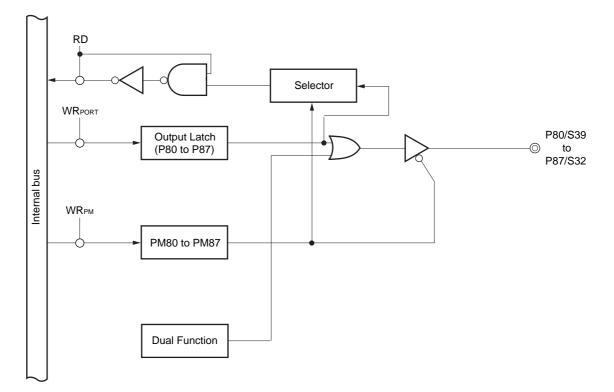

| 4.2.4 Port 8                                     | 85   |

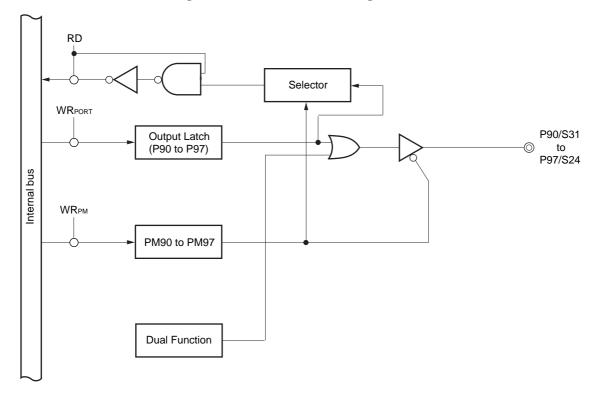

| 4.2.5 Port 9                                     | 86   |

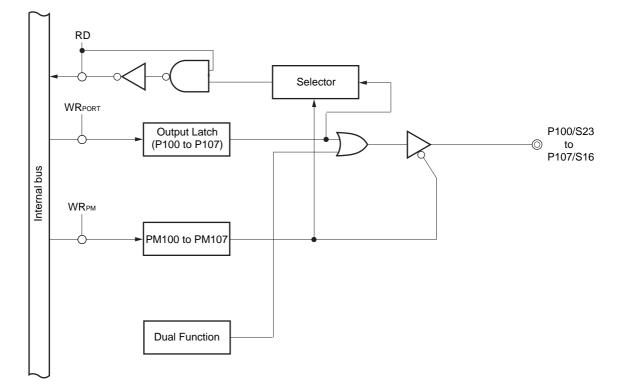

| 4.2.6 Port 10                                    | 87   |

| 4.2.7 Port 11                                    | 88   |

| 4.2.8 Port 12                                    | 89   |

| 4.3 Port Function Control Registers              | 90   |

| 4.4 Port Function Operations                     | 93   |

| 4.4.1 Writing to input/output port               | 93   |

| 4.4.2 Reading from input/output port             | 93   |

| 4.4.3 Operations on input/output port            | 93   |

| Chapter 5 Clock Generator                                             | 95  |

|-----------------------------------------------------------------------|-----|

| •                                                                     |     |

| 5.1 Clock Generator Functions                                         | 95  |

| 5.2 Clock Generator Configuration                                     | 96  |

| 5.3 Clock Generator Control Register                                  | 97  |

| 5.4 System Clock Oscillator                                           |     |

| 5.4.1 Main system clock oscillator                                    |     |

| 5.4.2 Subsystem clock oscillator                                      | 99  |

| 5.4.3 When no subsystem clocks are used                               |     |

| 5.5 Clock Generator Operations                                        | 102 |

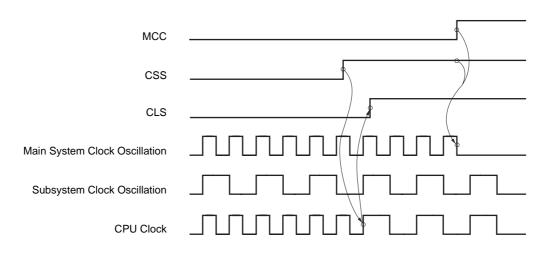

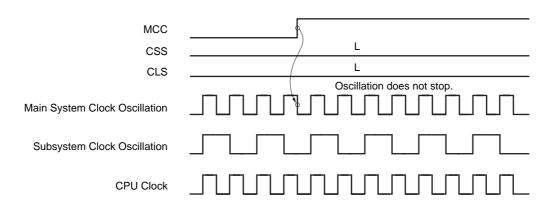

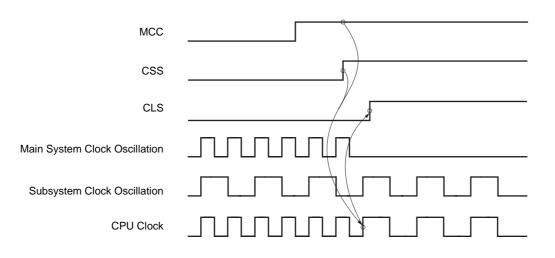

| 5.5.1 Main system clock operations                                    | 103 |

| 5.5.2 Subsystem clock operations                                      |     |

| 5.6 Changing System Clock and CPU Clock Settings                      |     |

| 5.6.1 Time required for switchover between system clock and CPU clock |     |

| 5.6.2 System clock and CPU clock switching procedure                  |     |

| 5.6.2 System clock and CPU clock switching procedure                  | 106 |

## Chapter 6 16-Bit Timer/ Event Counter ...... 108

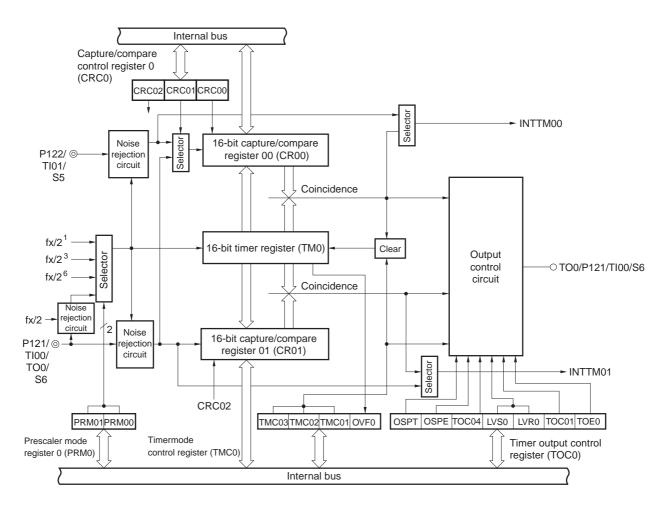

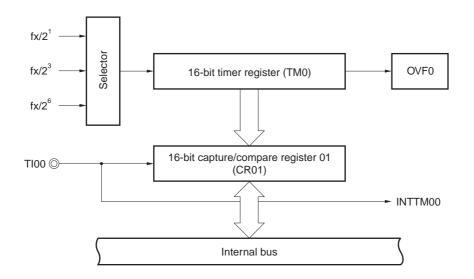

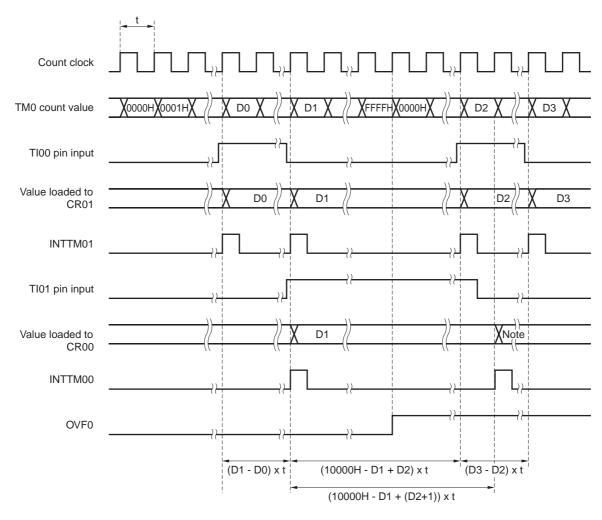

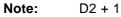

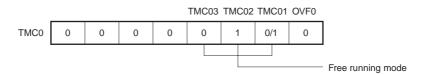

| 6.1 16-bit Timer/Event Counter Function              | 108 |

|------------------------------------------------------|-----|

| 6.2 16-bit Timer/Event Counter Configuration         | 109 |

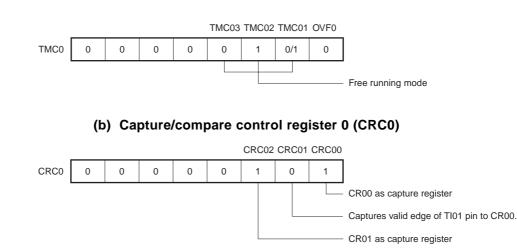

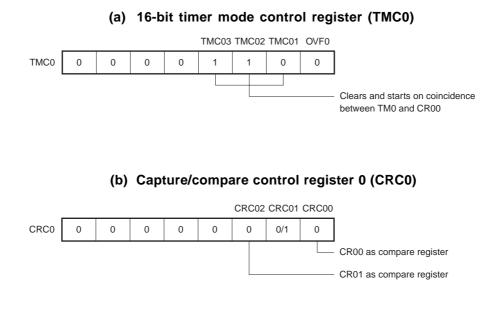

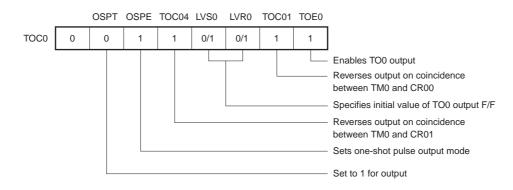

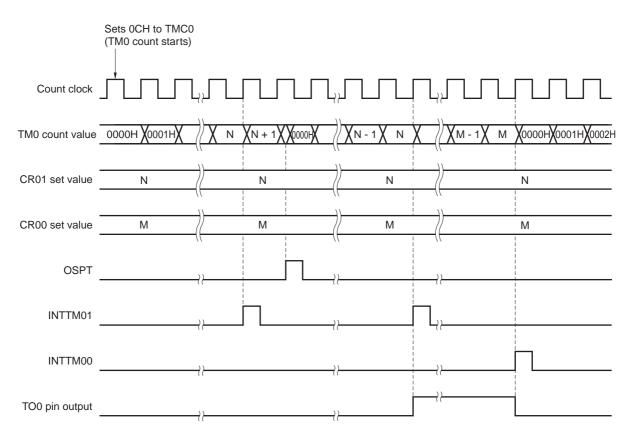

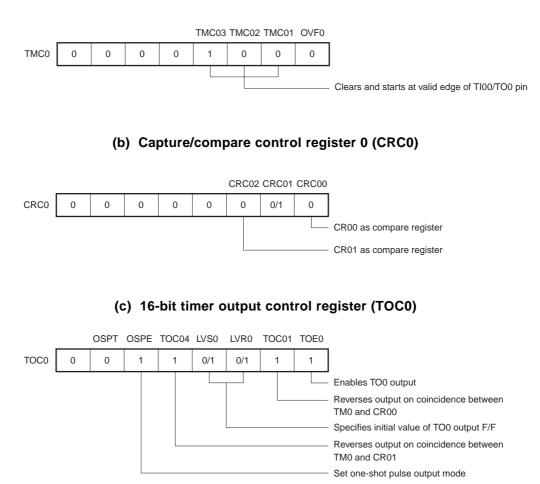

| 6.3 16-Bit Timer/Event Counter Control Register      | 113 |

| 6.4 16-Bit Timer/Event Counter Operations            | 120 |

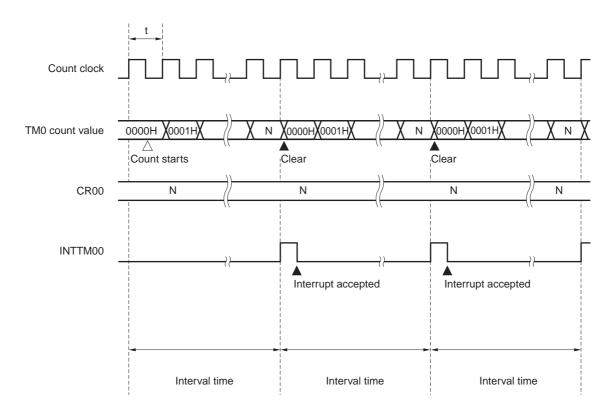

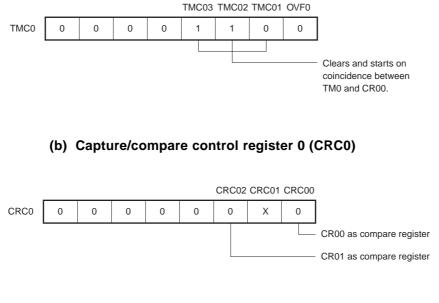

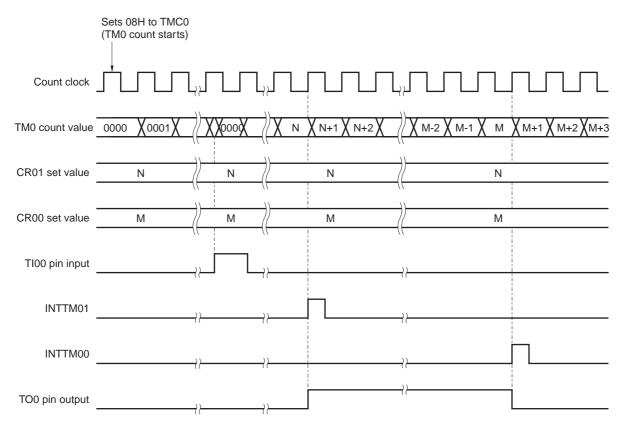

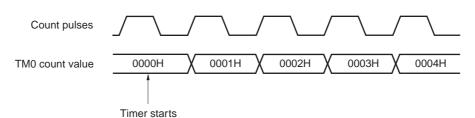

| 6.4.1 Operation as interval timer (16 bits)          | 120 |

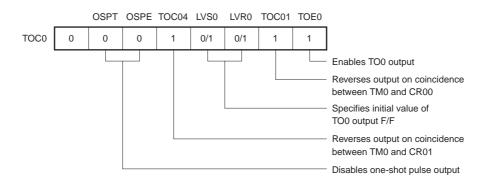

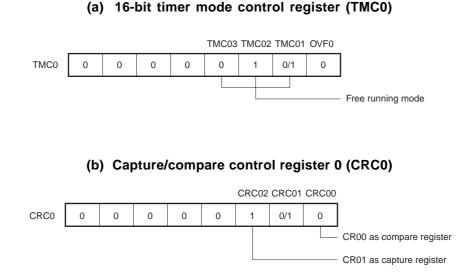

| 6.4.2 PPG output operation                           | 122 |

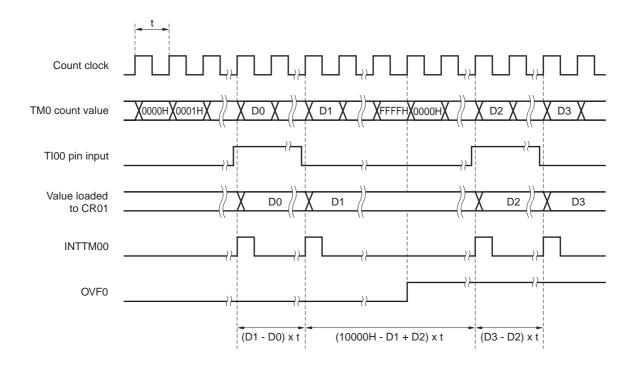

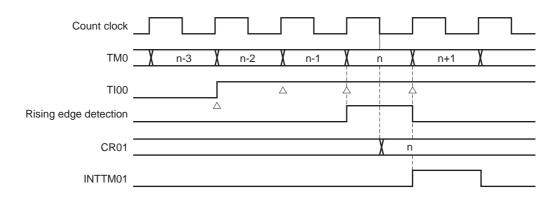

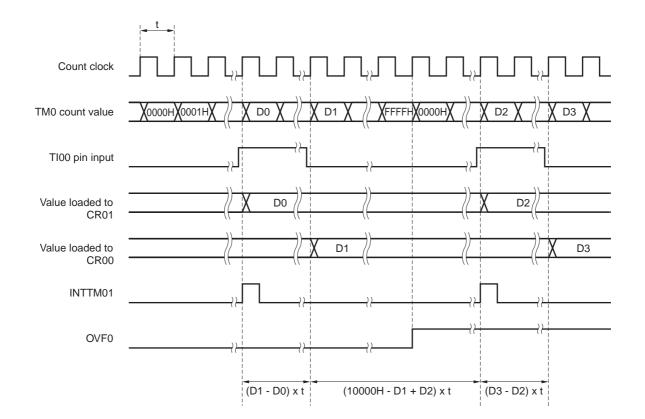

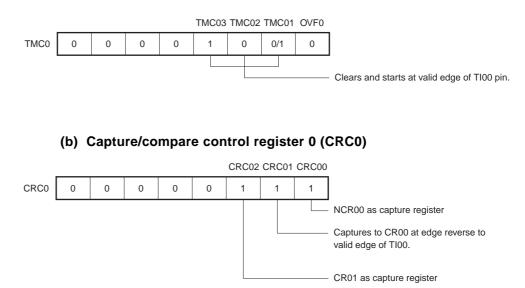

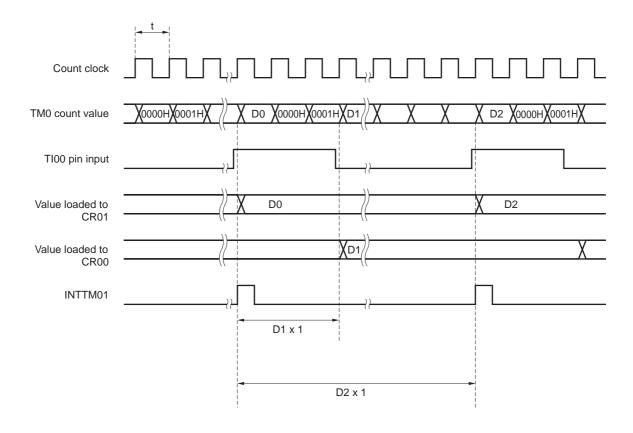

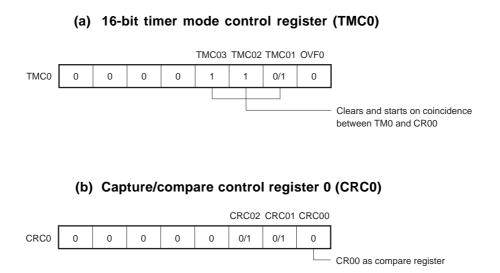

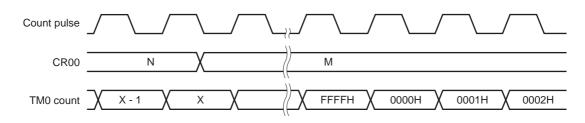

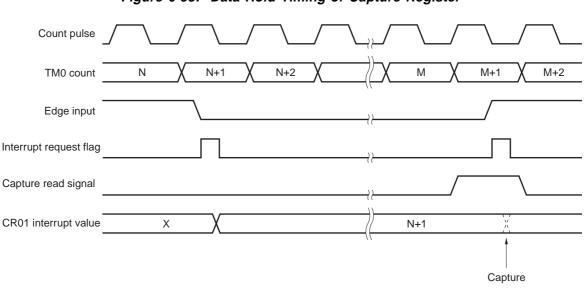

| 6.4.3 Pulse width measurement                        | 123 |

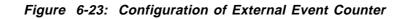

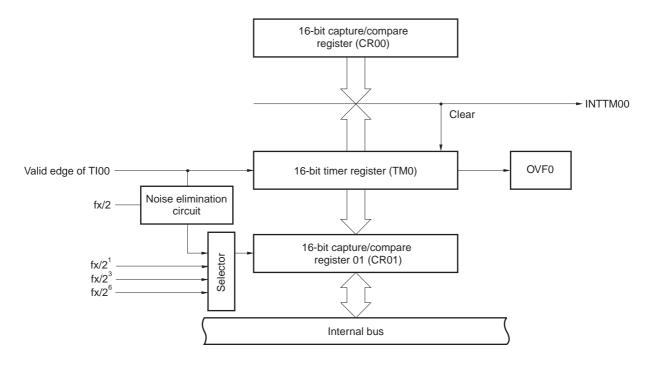

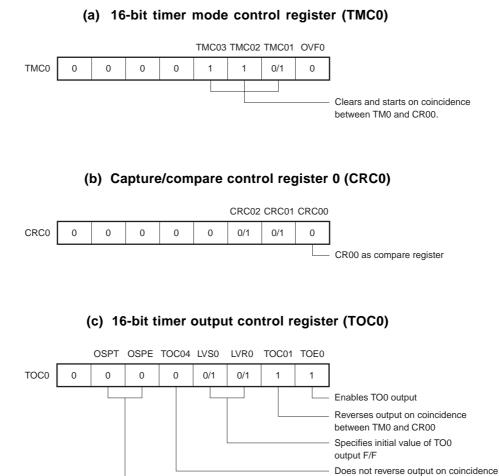

| 6.4.4 Operation as external event counter            | 130 |

| 6.4.5 Operation to output square wave                | 132 |

| 6.4.6 Operation to output one-shot pulse             | 134 |

| 6.5 16-Bit Timer/Event Counter Operating Precautions | 139 |

## Chapter 7 8-Bit Timer/Event Counters 50 and 51 ..... 143

| 7.1 8-Bit Timer/Event Counters 50 and 51 Functions         | 143 |

|------------------------------------------------------------|-----|

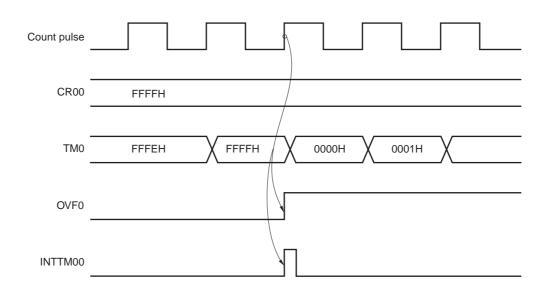

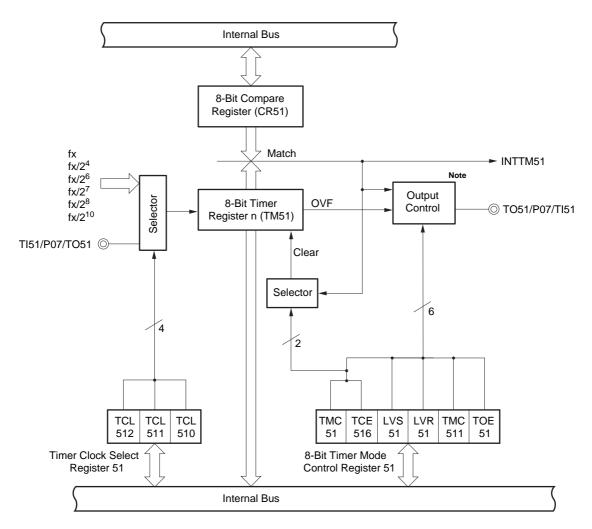

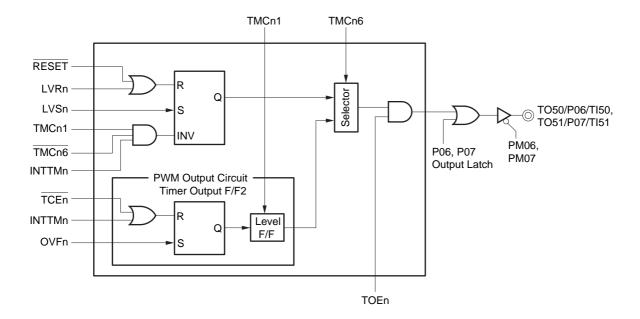

| 7.2 8-Bit Timer/Event Counters 50 and 51 Configurations    | 146 |

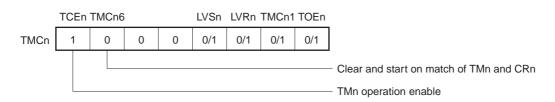

| 7.3 8-Bit Timer/Event Counters 50 and 51 Control Registers | 149 |

| 7.4 8-Bit Timer/Event Counters 50 and 51 Operations        | 154 |

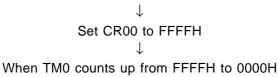

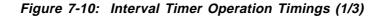

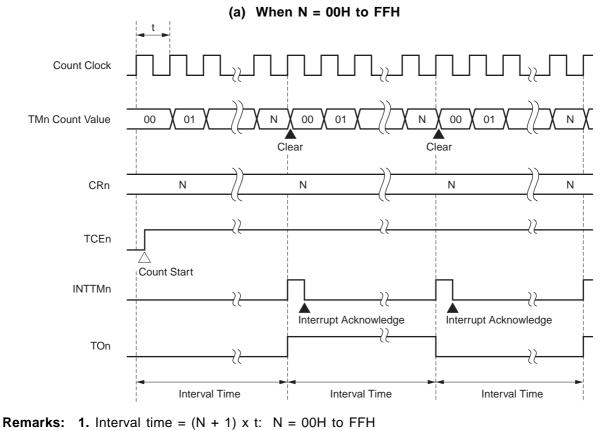

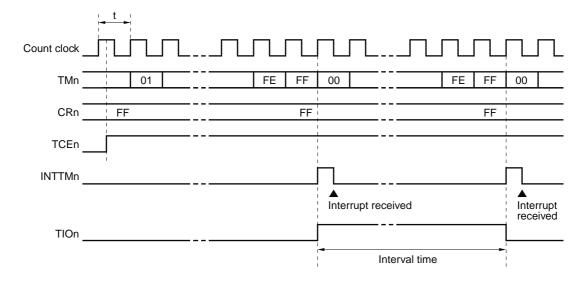

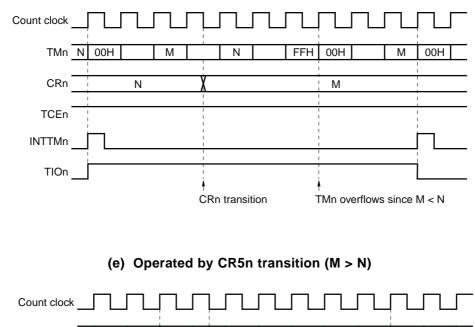

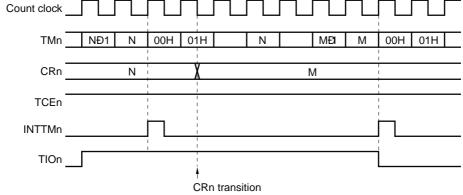

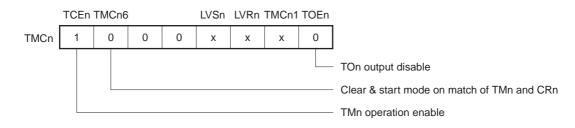

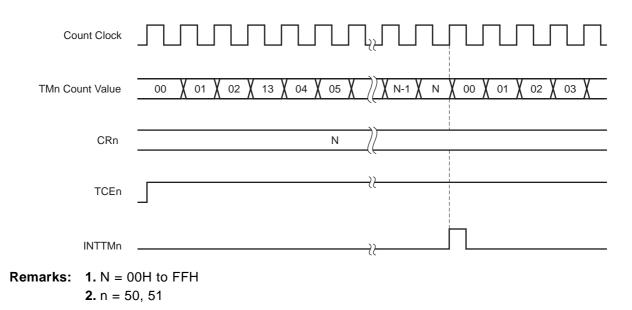

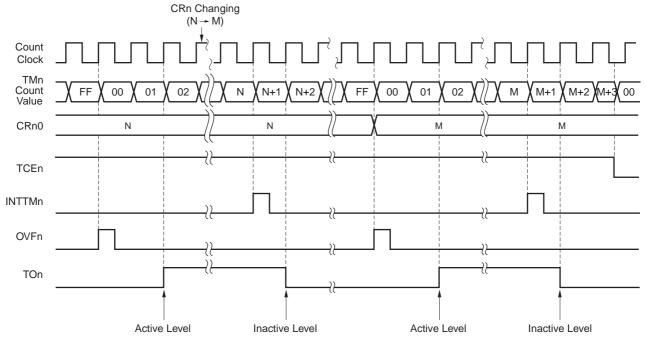

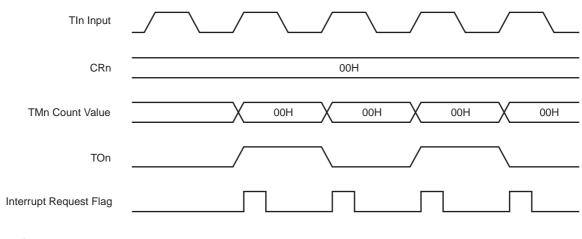

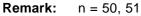

| 7.4.1 Interval timer operations                            | 154 |

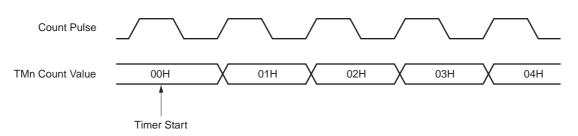

| 7.4.2 External event counter operation                     | 158 |

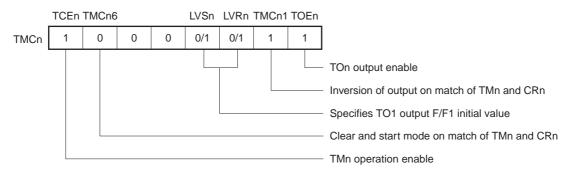

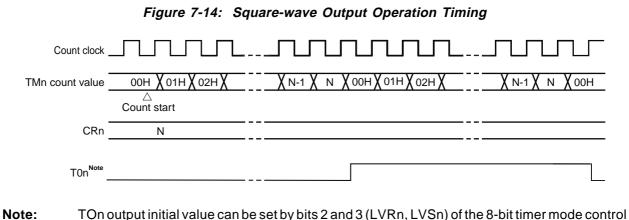

| 7.4.3 Square-wave output                                   | 159 |

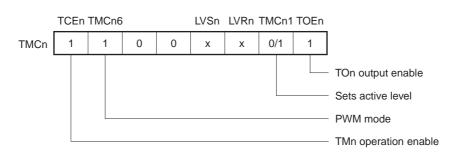

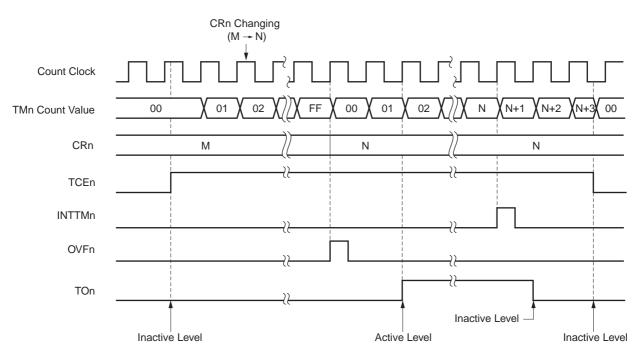

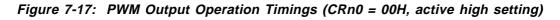

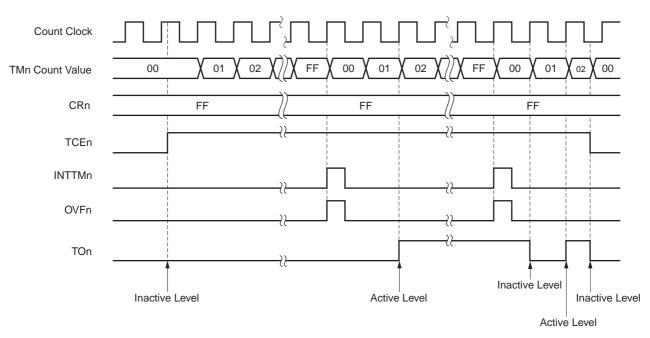

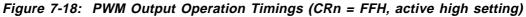

| 7.4.4 PWM output operations                                | 161 |

| 7.5 Cautions on 8-Bit Timer/Event Counters 50 and 51       | 164 |

| Chapter 8 Watch Timer                 |     |

|---------------------------------------|-----|

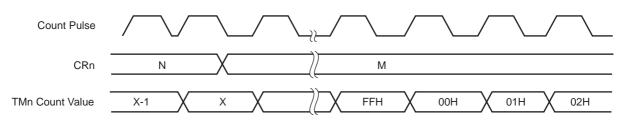

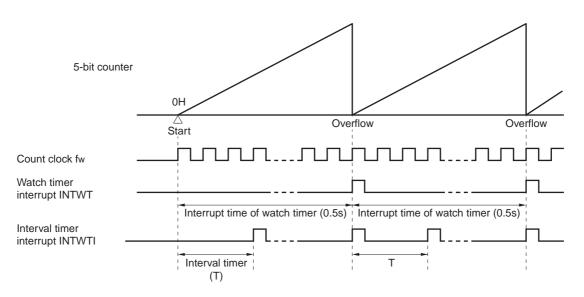

| 3.1 Watch Timer Functions 1           | 167 |

| 3.2 Watch Timer Configuration 1       | 168 |

| 3.3 Watch Timer Mode Register (WTM) 1 | 169 |

| 3.4 Watch Timer Operations 1          | 170 |

| 3.4.1 Watch timer operation 1         | 170 |

| 3.4.2 Interval timer operation 1      | 170 |

## Chapter 9 Watchdog Timer ...... 173

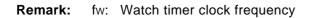

| 9.1   | Watchdog Timer Functions         | 173 |

|-------|----------------------------------|-----|

| 9.2   | Watchdog Timer Configuration     | 174 |

| 9.3   | Watchdog Timer Control Registers | 175 |

| 9.4 V | Vatchdog Timer Operations        | 177 |

| 9.4.1 | Watchdog timer operation         | 177 |

| 9.4.2 | 2 Interval timer operation       | 178 |

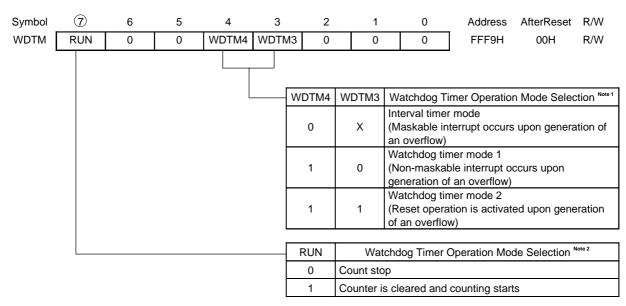

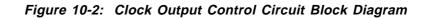

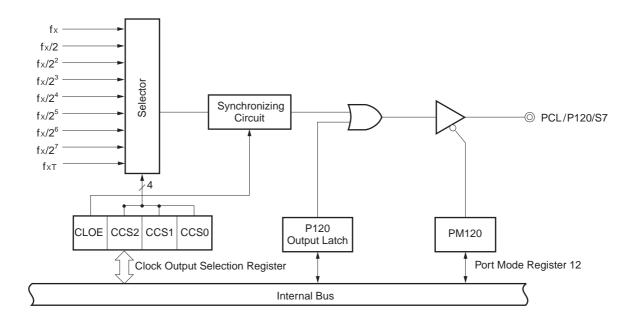

## Chapter 10 Clock Output Control Circuit ...... 180

| 10.1 | Clock Output Control Circuit Functions     | <b>180</b> |

|------|--------------------------------------------|------------|

| 10.2 | Clock Output Control Circuit Configuration | 181        |

| 10.3 | Clock Output Function Control Registers    | 182        |

##

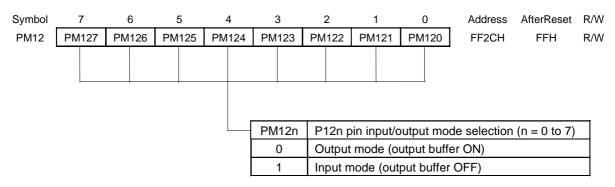

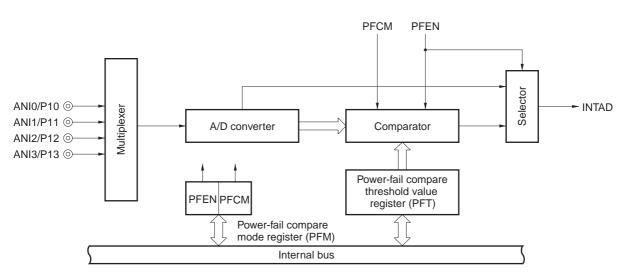

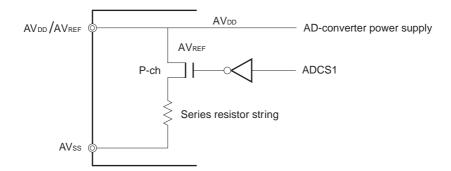

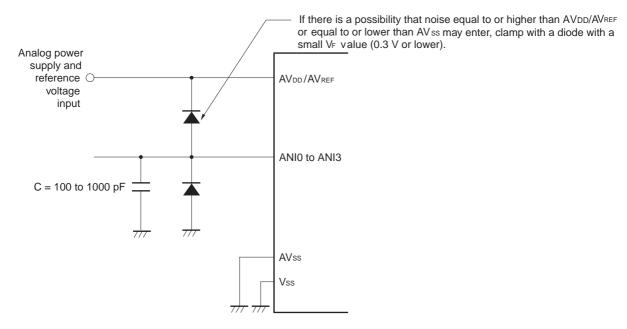

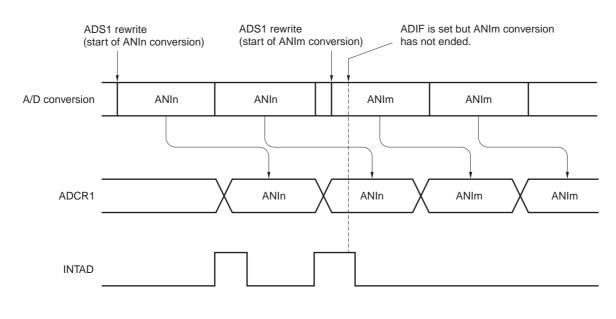

| 11.1 A/D Converter Functions 1                | 185 |

|-----------------------------------------------|-----|

| 11.2 A/D Converter Configuration 1            | 186 |

| 11.3 A/D Converter Control Registers 1        | 188 |

| 11.4 A/D Converter Operations 1               | 191 |

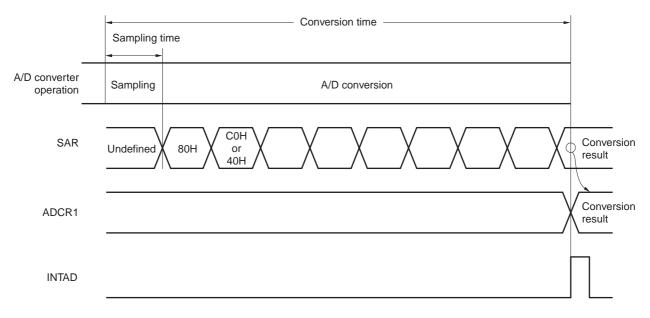

| 11.4.1 Basic operations of A/D converter 1    | 191 |

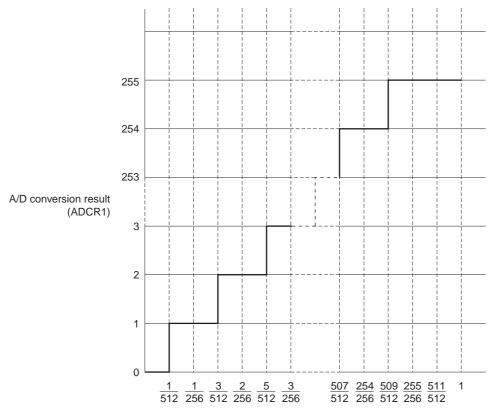

| 11.4.2 Input voltage and conversion results 1 | 193 |

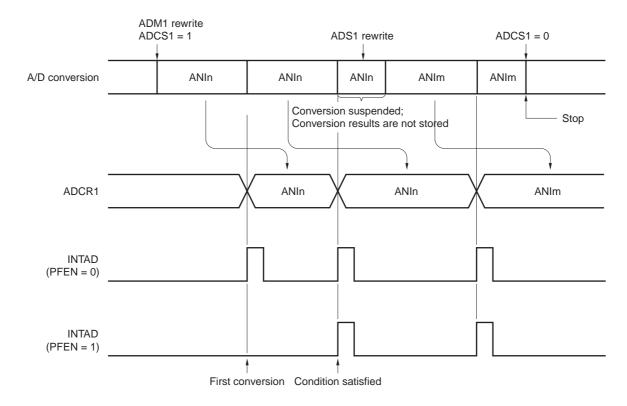

| 11.4.3 A/D converter operation mode 1         | 194 |

| 11.5 A/D Converter Precautions 1              | 196 |

| 11.6 Cautions on Emulation 1                  | 199 |

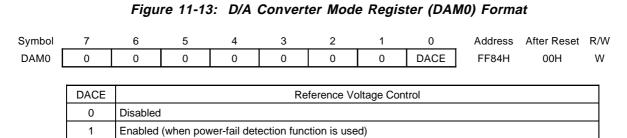

| 11.6.1 D/A converter mode register (DAM0) 1   | 199 |

| Chapter 12 Serial Interface Outline 2         | :01 |

| 12.1 Serial Interface Outline                 | 201 |

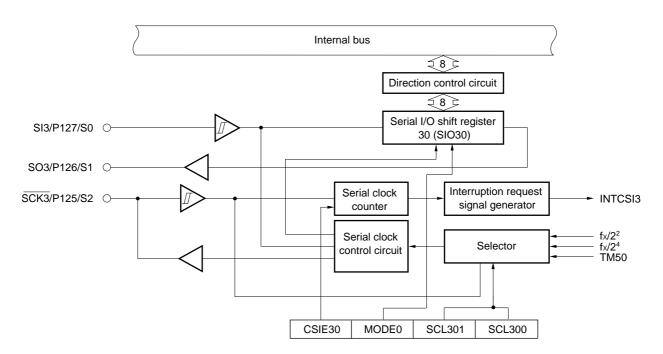

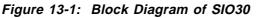

| Chapter 13 Serial Interface Channel 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 203                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 13.1 Serial Interface Channel 30 Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 203                                                                                                                      |

| 13.2 Serial Interface Channel 30 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 204                                                                                                                      |

| 13.3 List of SFRs (Special Function Registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| 13.4 Serial Interface Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 13.5 Serial Interface Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 13.5.1 Operation stop mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 206                                                                                                                      |

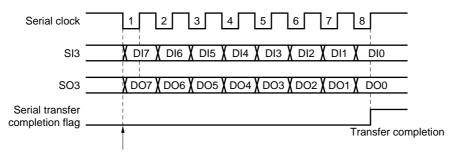

| 13.5.2 Three-wire serial I/O mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 207                                                                                                                      |

| Chapter 14 Serial Interface UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 210                                                                                                                        |

| 14.1 Serial Interface UART Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

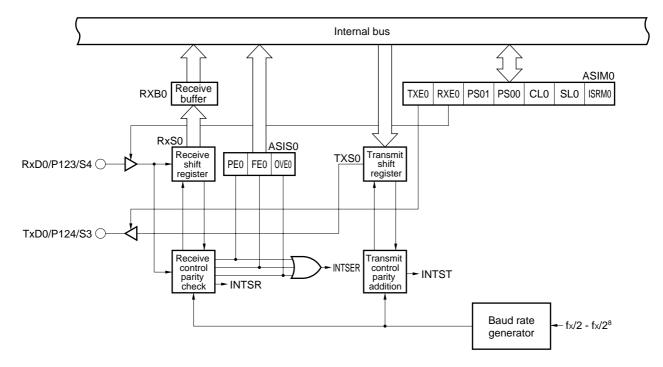

| 14.2 Serial Interface UART Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 14.3 List of SFRS (Special Function Registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

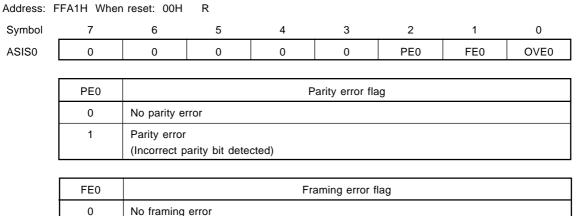

| 14.4 Serial Interface Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 212                                                                                                                      |

| 14.5 Serial Interface Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 216                                                                                                                      |

| 14.5.1 Operation stop mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 216                                                                                                                      |

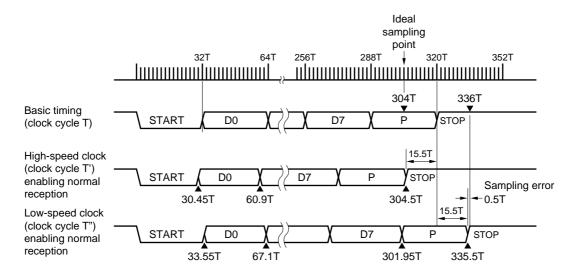

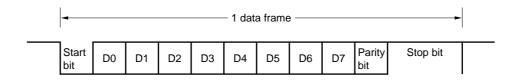

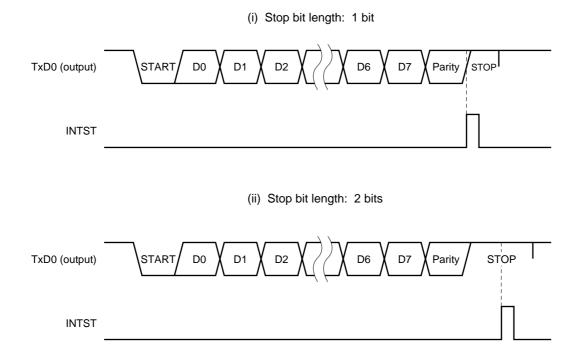

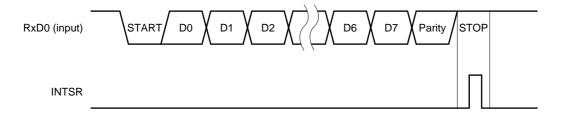

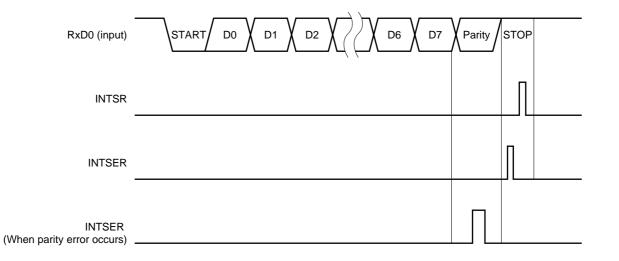

| 14.5.2 Asynchronous serial interface (UART) mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 14.6 Standby Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 228                                                                                                                      |

| Chapter 15 VAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 230                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

| 15.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| 15.2 Overview of the VAN Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 231                                                                                                                      |

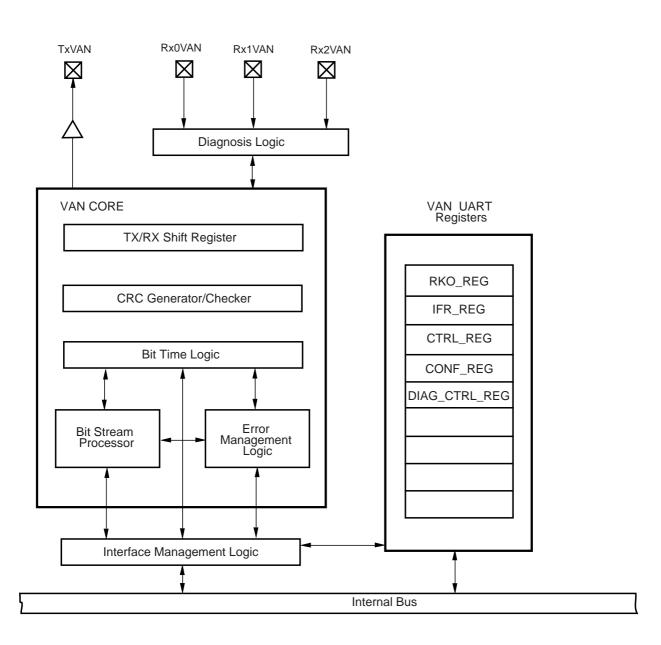

| 15.2 Overview of the VAN Bus<br>15.2.1 VAN UART Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 231<br>. 231                                                                                                             |

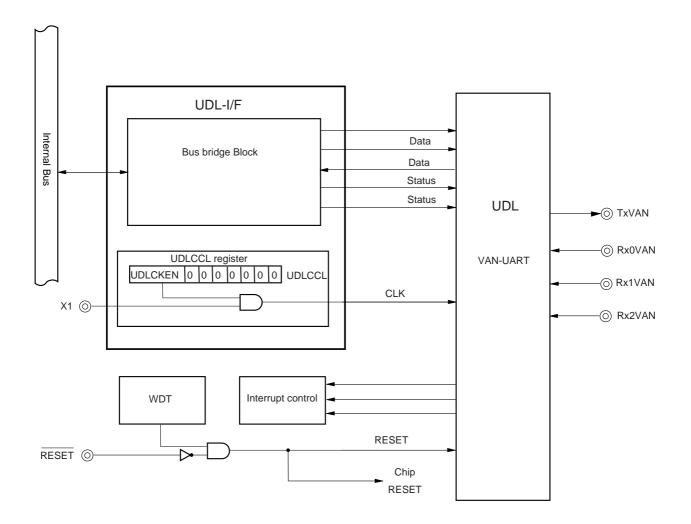

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 231<br>. 231<br>. 231                                                                                                    |

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> <li>15.3 Functional description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 231<br>. 231<br>. 231<br>. 235                                                                                           |

| <ul> <li>15.2 Overview of the VAN Bus</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 231<br>. 231<br>. 231<br>. 235<br>. 235                                                                                  |

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> <li>15.3 Functional description</li> <li>15.3.1 Overview of the VAN UART Registers</li> <li>15.3.2 Autonomous mode functions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 231<br>231<br>231<br>235<br>235<br>235<br>236                                                                              |

| <ul> <li>15.2 Overview of the VAN Bus</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 231<br>. 231<br>. 231<br>. 235<br>. 235<br>. 236<br>. 236                                                                |

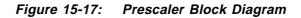

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> <li>15.3 Functional description</li> <li>15.3.1 Overview of the VAN UART Registers</li> <li>15.3.2 Autonomous mode functions</li> <li>15.3.2.1 Autonomous mode features</li> <li>15.3.2.2 Programming of the prescaler in Rank 0 transmission (SOF included)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 231<br>231<br>231<br>235<br>235<br>235<br>236<br>236<br>236                                                                |

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> <li>15.3 Functional description</li> <li>15.3.1 Overview of the VAN UART Registers</li> <li>15.3.2 Autonomous mode functions</li> <li>15.3.2.1 Autonomous mode features</li> <li>15.3.2.2 Programming of the prescaler in Rank 0 transmission (SOF included)</li> <li>15.3.2.3 Transmission features in autonomous mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>236<br>236                                                         |

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> <li>15.3 Functional description</li> <li>15.3.1 Overview of the VAN UART Registers</li> <li>15.3.2 Autonomous mode functions</li> <li>15.3.2.1 Autonomous mode features</li> <li>15.3.2.2 Programming of the prescaler in Rank 0 transmission (SOF included)</li> <li>15.3.2.3 Transmission features in autonomous mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>236<br>237<br>238                                                  |

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> <li>15.3 Functional description</li> <li>15.3.1 Overview of the VAN UART Registers</li> <li>15.3.2 Autonomous mode functions</li> <li>15.3.2.1 Autonomous mode features</li> <li>15.3.2.2 Programming of the prescaler in Rank 0 transmission (SOF included)</li> <li>15.3.2.3 Transmission features in autonomous mode</li> <li>15.3.3 Synchronous mode features</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>236<br>237<br>238                                                  |

| <ul> <li>15.2 Overview of the VAN Bus</li> <li>15.2.1 VAN UART Description</li> <li>15.2.2 VAN UART Interface</li> <li>15.3 Functional description</li> <li>15.3.1 Overview of the VAN UART Registers</li> <li>15.3.2 Autonomous mode functions</li> <li>15.3.2.1 Autonomous mode features</li> <li>15.3.2.2 Programming of the prescaler in Rank 0 transmission (SOF included)</li> <li>15.3.2.3 Transmission features in autonomous mode</li> <li>15.3.4 Synchronous mode features</li> <li>15.3.5 Synchronous mode features</li> <li>15.3.5 Synchronous mode features</li> </ul>                                                                                                                                                                                                                                                                                                                                                         | 231<br>231<br>235<br>235<br>236<br>236<br>236<br>236<br>237<br>238<br>238<br>238                                           |

| 15.2       Overview of the VAN Bus         15.2.1       VAN UART Description         15.2.2       VAN UART Interface         15.3       Functional description         15.3.1       Overview of the VAN UART Registers         15.3.2       Autonomous mode functions         15.3.2.1       Autonomous mode features         15.3.2.2       Programming of the prescaler in Rank 0 transmission (SOF included)         15.3.2.3       Transmission features in autonomous mode         15.3.3       Synchronous mode features         15.3.3.1       Synchronous mode features         15.3.3.2       Transmission features in synchronous mode         15.3.3.4       Handling of a collision                                                                                                                                                                                                                                             | 231<br>231<br>235<br>235<br>236<br>236<br>236<br>236<br>236<br>238<br>238<br>238<br>238                                    |

| 15.2       Overview of the VAN Bus         15.2.1       VAN UART Description         15.2.2       VAN UART Interface         15.3       Functional description         15.3.1       Overview of the VAN UART Registers         15.3.2       Autonomous mode functions         15.3.2.1       Autonomous mode features         15.3.2.1       Autonomous mode features         15.3.2.2       Programming of the prescaler in Rank 0 transmission (SOF included)         15.3.2.3       Transmission features in autonomous mode         15.3.3       Synchronous mode features         15.3.3.1       Synchronous mode features         15.3.3.2       Transmission features in synchronous mode         15.3.4       Handling of a collision         15.3.5       Executing the CRC                                                                                                                                                        | 231<br>231<br>235<br>235<br>236<br>236<br>236<br>236<br>237<br>238<br>238<br>238<br>238<br>238                             |

| 15.2       Overview of the VAN Bus         15.2.1       VAN UART Description         15.2.2       VAN UART Interface         15.3       Functional description         15.3.1       Overview of the VAN UART Registers         15.3.2       Autonomous mode functions         15.3.2.1       Autonomous mode features         15.3.2.2       Programming of the prescaler in Rank 0 transmission (SOF included)         15.3.2.3       Transmission features in autonomous mode         15.3.3       Synchronous mode features         15.3.3.1       Synchronous mode features         15.3.3.2       Transmission features in synchronous mode         15.3.3.4       Handling of a collision         15.3.5       Executing the CRC         15.3.5.1       CRC transmission                                                                                                                                                              | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238               |

| 15.2       Overview of the VAN Bus         15.2.1       VAN UART Description         15.2.2       VAN UART Interface         15.3       Functional description         15.3.1       Overview of the VAN UART Registers         15.3.2       Autonomous mode functions         15.3.2.1       Autonomous mode features         15.3.2.2       Programming of the prescaler in Rank 0 transmission (SOF included)         15.3.2.3       Transmission features in autonomous mode         15.3.3       Synchronous mode functions         15.3.3.1       Synchronous mode features         15.3.3.2       Transmission features in autonomous mode         15.3.3.1       Synchronous mode functions         15.3.3.2       Transmission features in synchronous mode         15.3.4       Handling of a collision         15.3.5       Executing the CRC         15.3.5.1       CRC transmission         15.3.5.2       Reception of the CRC | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238        |

| 15.2       Overview of the VAN Bus         15.2.1       VAN UART Description         15.2.2       VAN UART Interface         15.3       Functional description         15.3.1       Overview of the VAN UART Registers         15.3.2       Autonomous mode functions         15.3.2.1       Autonomous mode features         15.3.2.2       Programming of the prescaler in Rank 0 transmission (SOF included)         15.3.2.3       Transmission features in autonomous mode         15.3.3.1       Synchronous mode features         15.3.3.3       Synchronous mode features         15.3.3.4       Handling of a collision         15.3.5       Executing the CRC         15.3.5.1       CRC transmission         15.3.5.2       Reception of the CRC         15.3.5.3       Gontrol of the acknowledge bit                                                                                                                           | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238 |

| 15.2       Overview of the VAN Bus         15.2.1       VAN UART Description         15.2.2       VAN UART Interface         15.3       Functional description         15.3.1       Overview of the VAN UART Registers         15.3.2       Autonomous mode functions         15.3.2.1       Autonomous mode features         15.3.2.2       Programming of the prescaler in Rank 0 transmission (SOF included)         15.3.2.3       Transmission features in autonomous mode         15.3.3       Synchronous mode features         15.3.3.1       Synchronous mode features         15.3.3.2       Transmission features in synchronous mode         15.3.3.4       Handling of a collision         15.3.5       Executing the CRC         15.3.5.1       CRC transmission         15.3.5.2       Reception of the CRC         15.3.5.2       Reception of the CRC         15.3.5.3       Ferror control and Interrupt control          | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238 |

| 15.2       Overview of the VAN Bus         15.2.1       VAN UART Description         15.2.2       VAN UART Interface         15.3       Functional description         15.3.1       Overview of the VAN UART Registers         15.3.2       Autonomous mode functions         15.3.2.1       Autonomous mode features         15.3.2.2       Programming of the prescaler in Rank 0 transmission (SOF included)         15.3.2.3       Transmission features in autonomous mode         15.3.3.1       Synchronous mode features         15.3.3.3       Synchronous mode features         15.3.3.4       Handling of a collision         15.3.5       Executing the CRC         15.3.5.1       CRC transmission         15.3.5.2       Reception of the CRC         15.3.5.3       Gontrol of the acknowledge bit                                                                                                                           | 231<br>231<br>235<br>235<br>235<br>236<br>236<br>236<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238<br>238 |

| 15.4 VAN UART Registers                                                | . 243 |

|------------------------------------------------------------------------|-------|

| 15.4.1 Rank0 Transmission Register (RK0_REG)                           | . 244 |

| 15.4.2 In Frame Response Register (IFR_REG)                            | . 245 |

| 15.4.3 Control Register (CTRL_REG)                                     | . 247 |

| 15.4.4 Configuration Register (CONF_REG)                               | 250   |

| 15.4.5 Diagnosis Control Register (DIAG_CTRL_REG)                      | 253   |

| 15.4.6 Mask1 registers (MSK1_MSB_REG, MSK1_LSB_REG)                    | 256   |

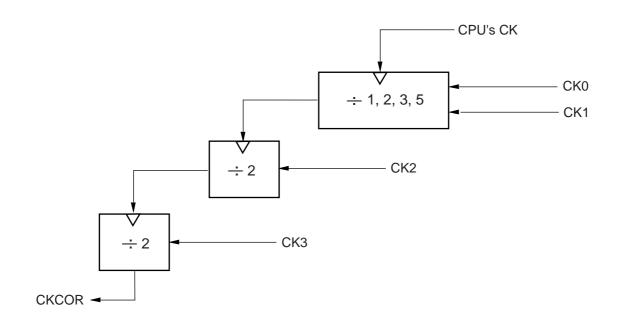

| 15.4.7 Acceptance Code 1 registers (AC1_MSB_REG, AC1_LSB_REG)          | 257   |

| 15.4.8 Mask2 registers (MSK2_MSB_REG, MSK2_LSB_REG)                    | 258   |

| 15.4.9 Acceptance Code 2, 3 and 4 Registers (AC2_MSB_REG, AC2_LSB_REG, | 259   |

| 15.4.10 Status Register (STAT_REG)                                     | 260   |

| 15.4.11 Receive register (REC_REG)                                     | . 262 |

| 15.4.12 Diagnosis Status Register (DIAG_STAT_REG)                      | 263   |

| 15.4.13 Interrupt enable register (INT_ENABLE_REG)                     | 264   |

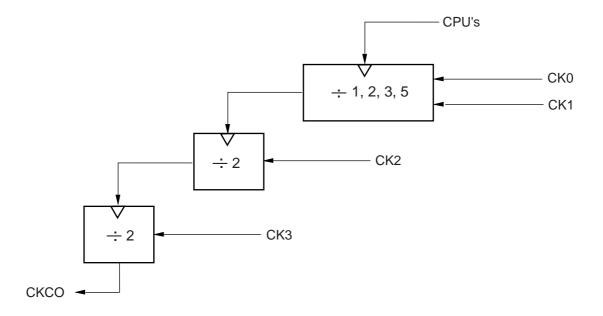

| 15.4.14 VAN clock selection register (UDLCCL)                          | 266   |

| 15.5 VAN UART initialisation                                           | . 267 |

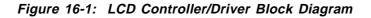

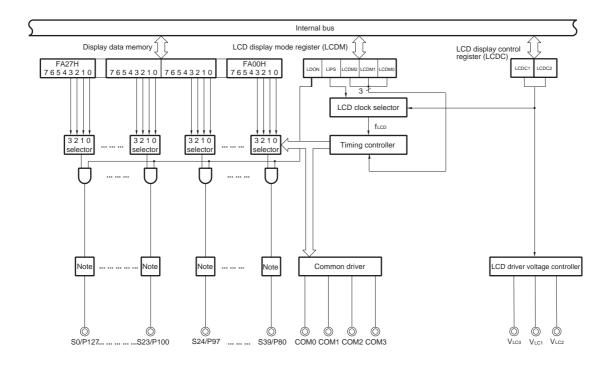

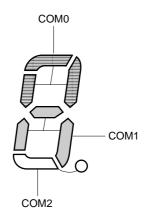

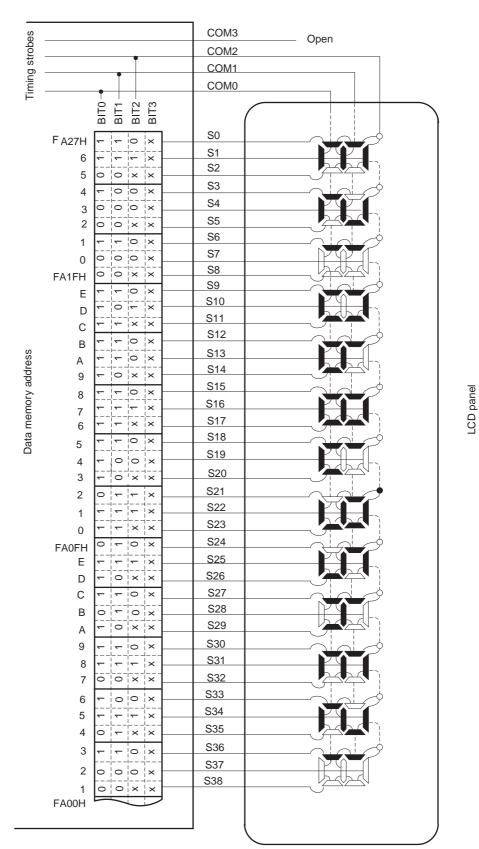

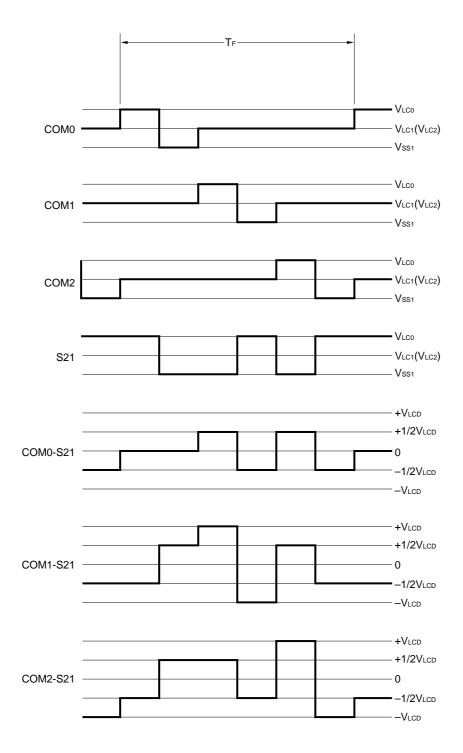

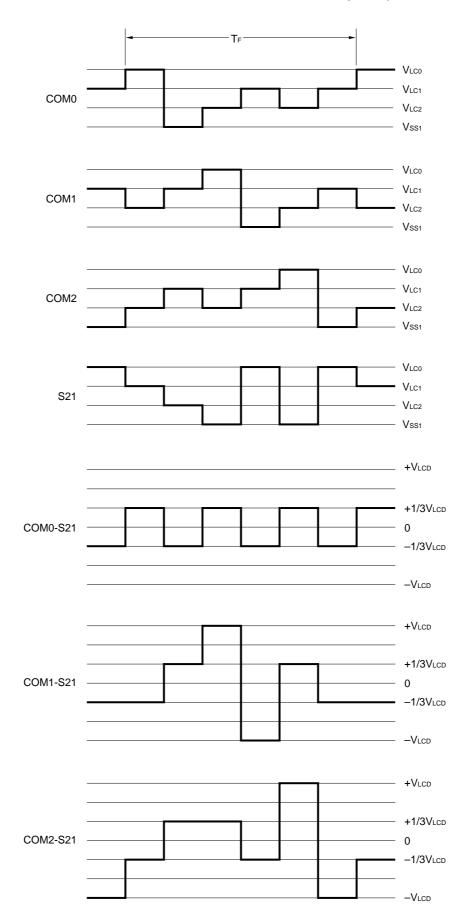

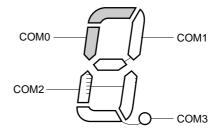

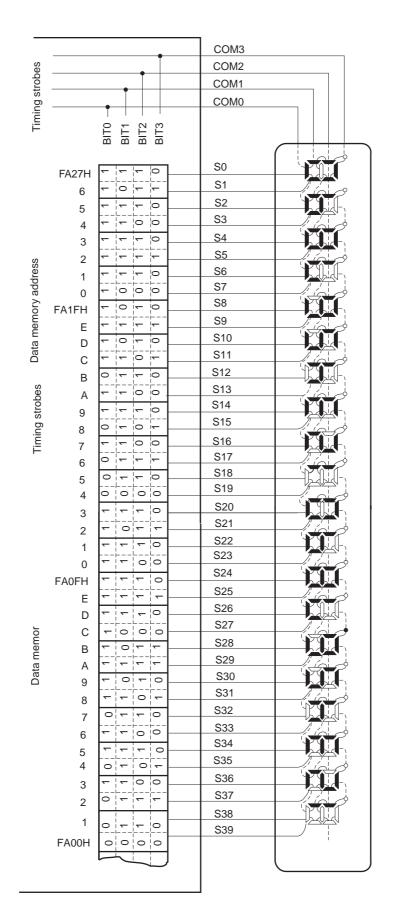

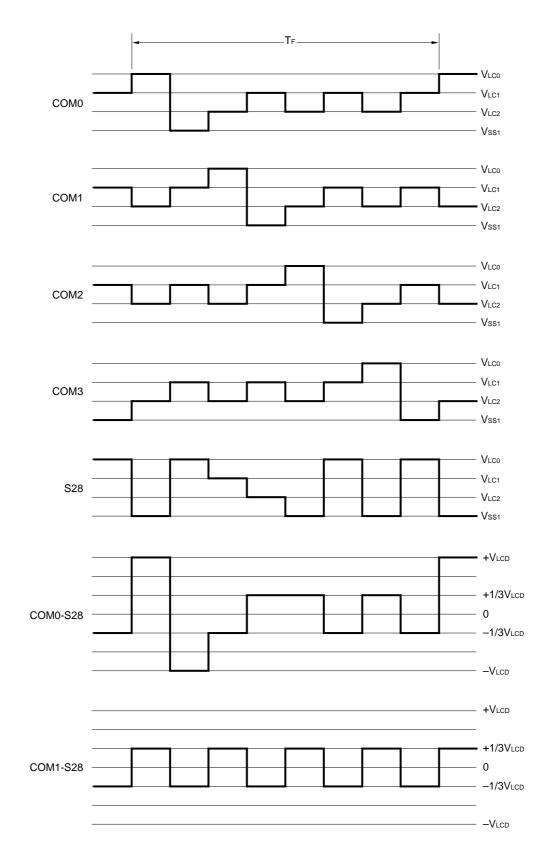

| Chapter 16 LCD Controller/Driver                                       | 269   |

| 16.1 LCD Controller/Driver Functions                                   |       |

| 16.2 LCD Controller/Driver Configuration                               |       |

| 16.3 LCD Controller/Driver Control Registers                           |       |

| 16.4 LCD Controller/Driver Settings                                    |       |

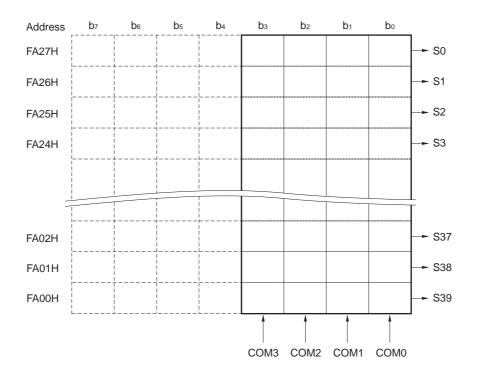

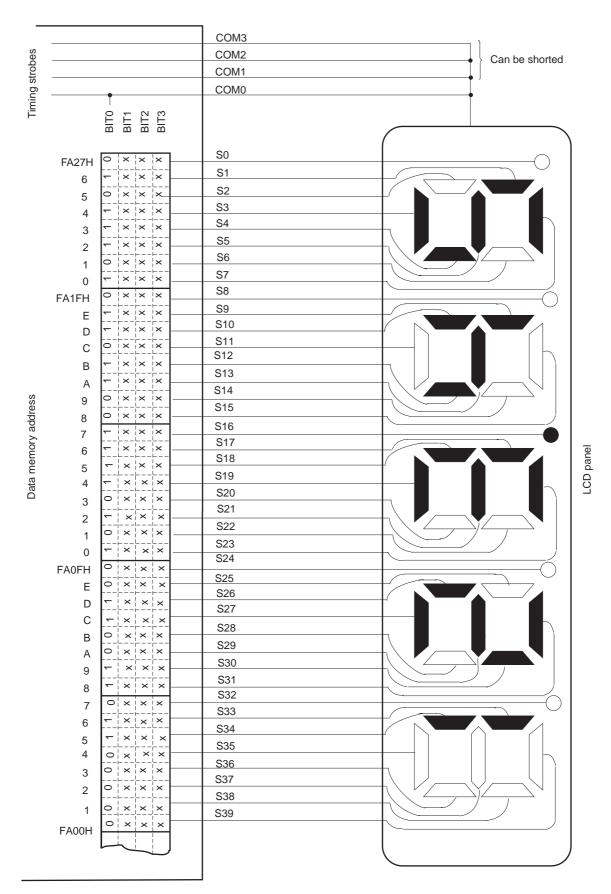

| 16.5 LCD Display Data Memory                                           |       |

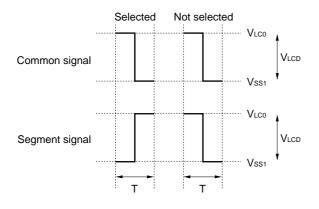

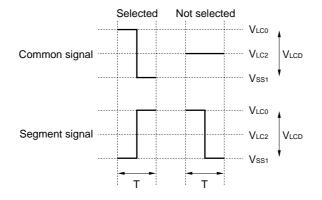

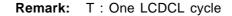

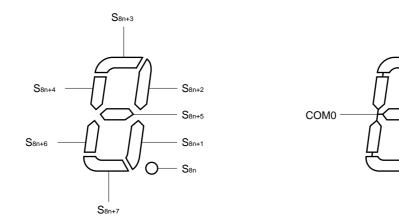

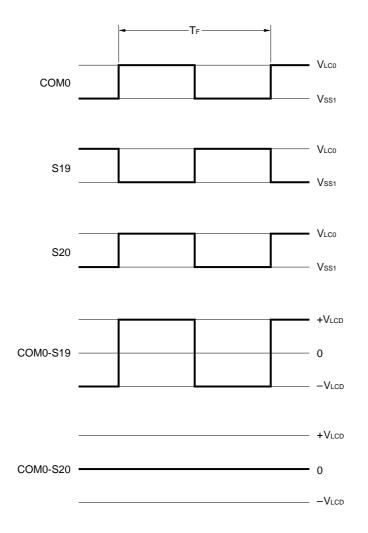

| 16.6 Common Signals and Segment Signals                                |       |

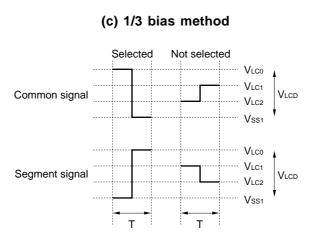

| 16.7 Supply of LCD Drive Voltages VLC0, VLC1, VLC2                     |       |

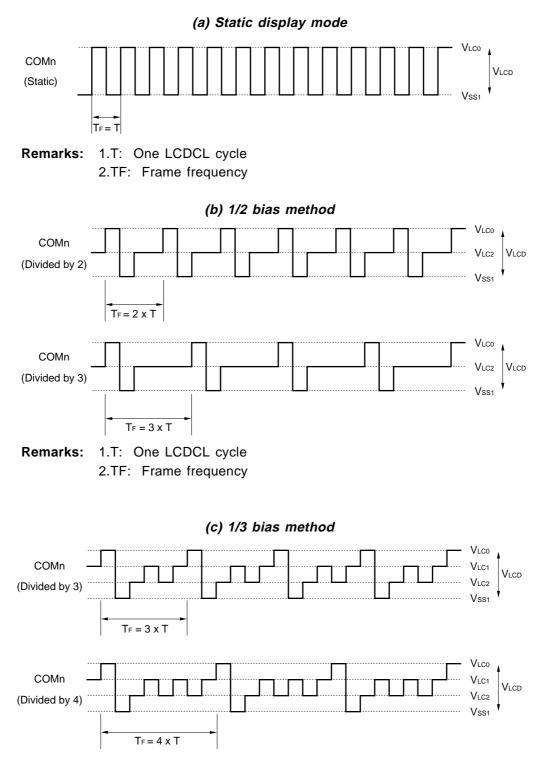

| 16.8 Display Modes                                                     |       |

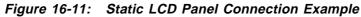

| 16.8.1 Static display example                                          |       |

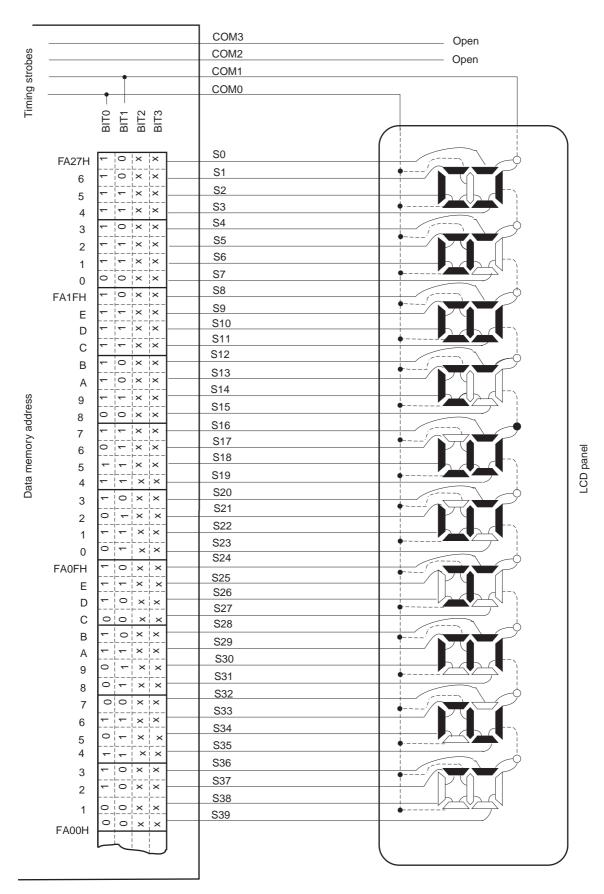

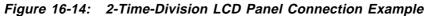

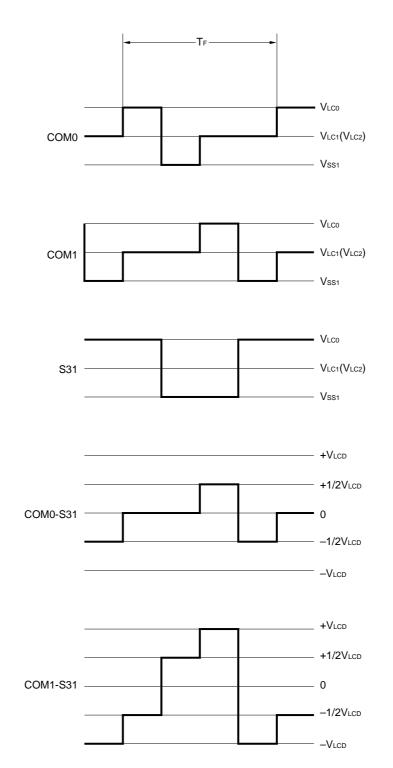

| 16.8.2 2-time-division display example                                 |       |

| 16.8.3 3-time-division display example                                 |       |

| 16.8.4 4-time-division display example                                 | . 294 |

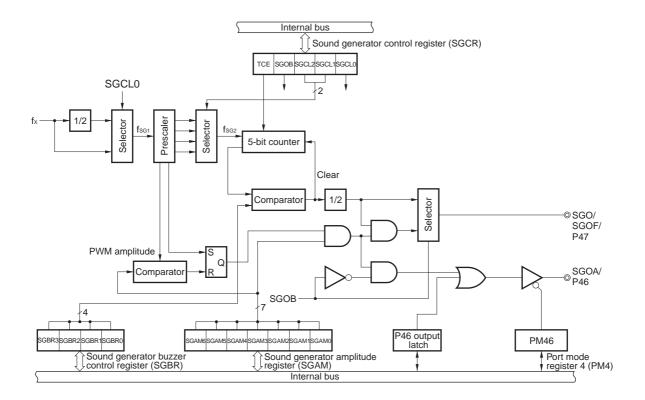

| Chapter 17 Sound Generator                                             | 298   |

| 17.1 Sound Generator Function                                          |       |

| 17.2 Sound Generator Configuration                                     |       |

| 17.3 Sound Generator Control Registers                                 |       |

| 17.4 Sound Generator Operations                                        |       |

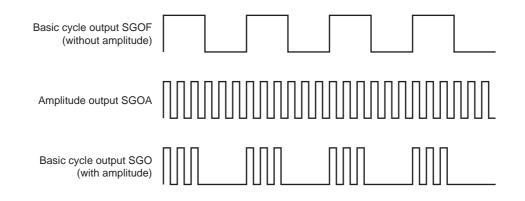

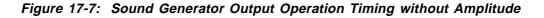

| 17.4.1 To output basic cycle signal SGOF (without amplitude)           |       |

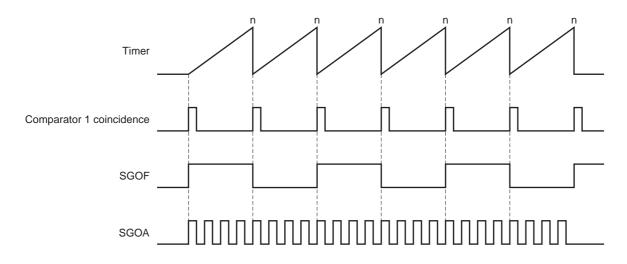

| 17.4.2 To output basic cycle signal SGO (with amplitude)               | 305   |

| hapter 18 Interrupt Functions                             | 7  |

|-----------------------------------------------------------|----|

| .1 Interrupt Function Types                               | )7 |

| .2 Interrupt Sources and Configuration 30                 | 8  |

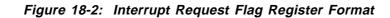

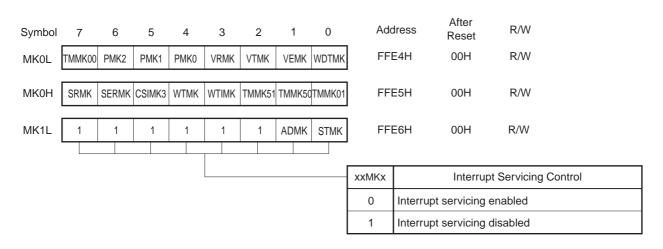

| .3 Interrupt Function Control Registers 31                | 1  |

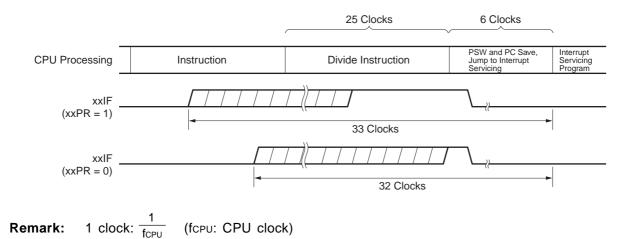

| .4 Interrupt Servicing Operations 31                      | 7  |

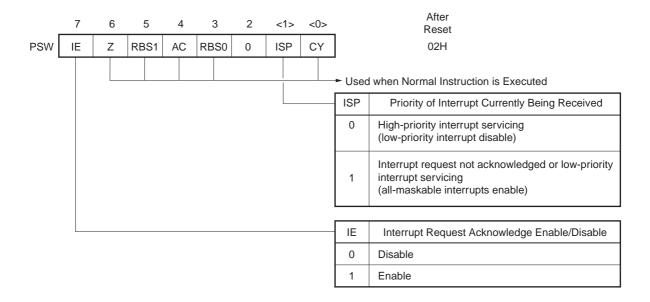

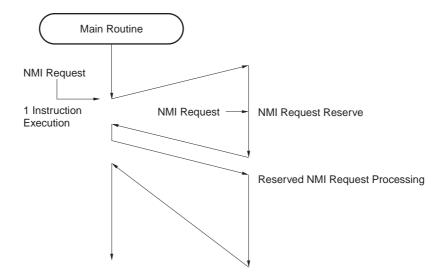

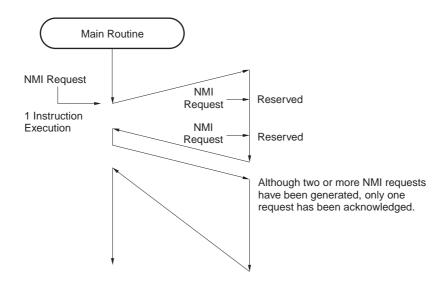

| .4.1 Non-maskable interrupt request acknowledge operation | 7  |

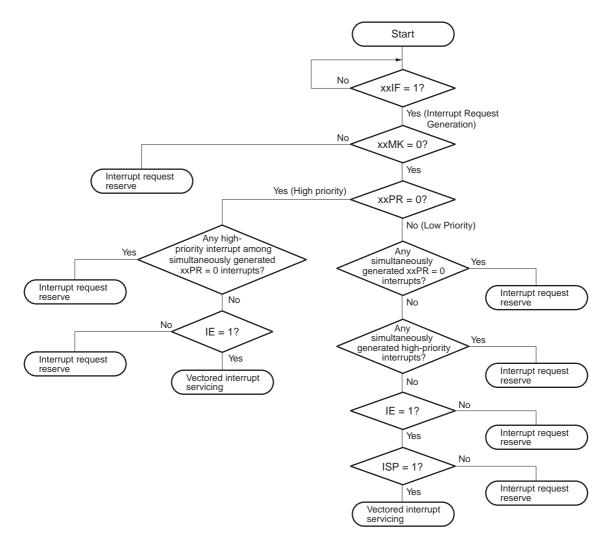

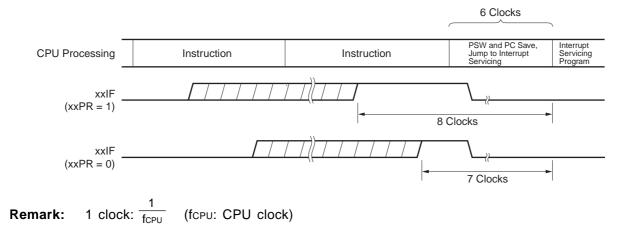

| .4.2 Maskable interrupt request acknowledge operation 32  | :0 |

| .4.3 Software interrupt request acknowledge operation 32  | 2  |

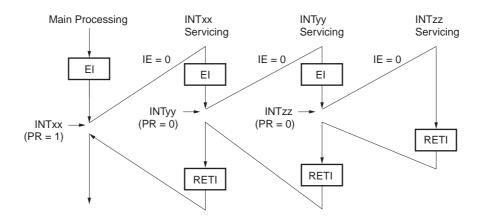

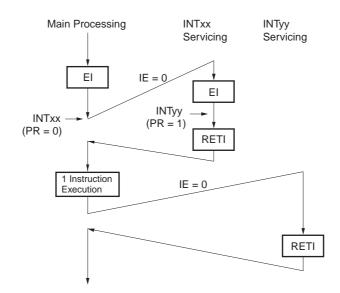

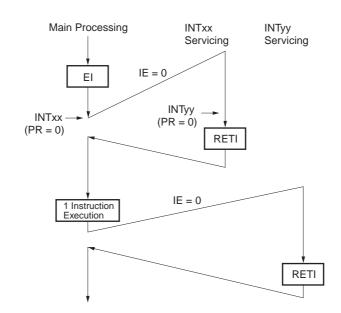

| .4.4 Multiple interrupt servicing                         | :3 |

| .4.5 Interrupt request reserve                            | 6  |

| Chapter 19 Standby Function 3                       | 328 |

|-----------------------------------------------------|-----|

| 19.1 Standby Function and Configuration             | 328 |

| 19.1.1 Standby function                             | 328 |

| 19.1.2 Standby function control register            | 329 |

| 19.2 Standby Function Operations                    | 330 |

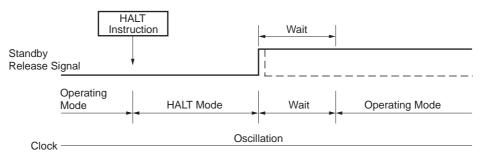

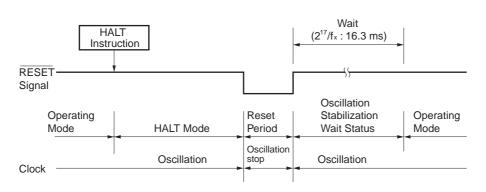

| 19.2.1 HALT mode                                    | 330 |

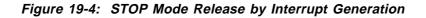

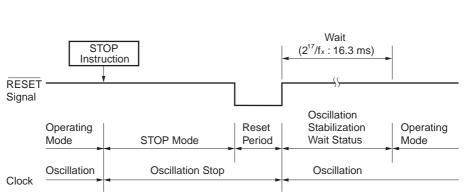

| 19.2.2 STOP mode                                    | 333 |

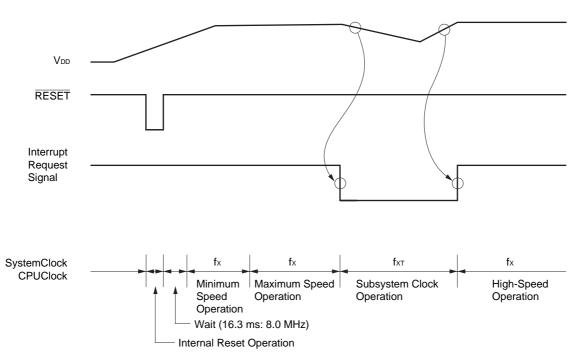

| Chapter 20 Reset Function 3                         | 37  |

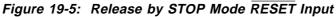

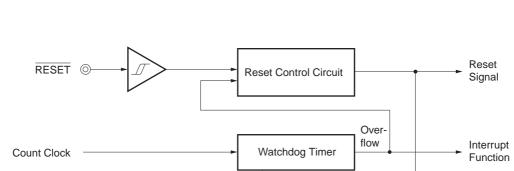

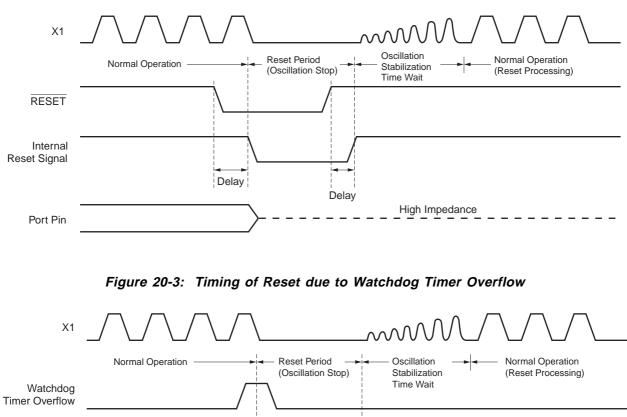

| 20.1 Reset Function                                 | 337 |

| Chapter 21 µPD16F15 3                               | 342 |

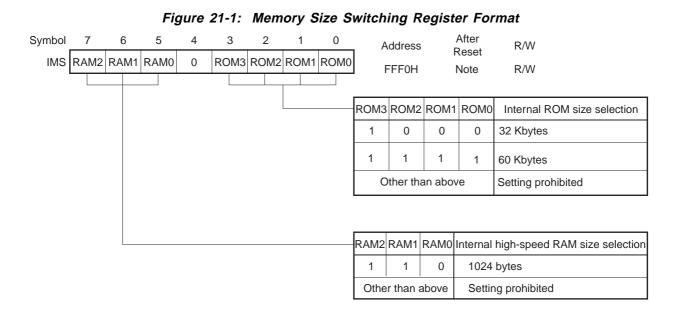

| 21.1 Memory Size Switching Register (IMS)           | 343 |

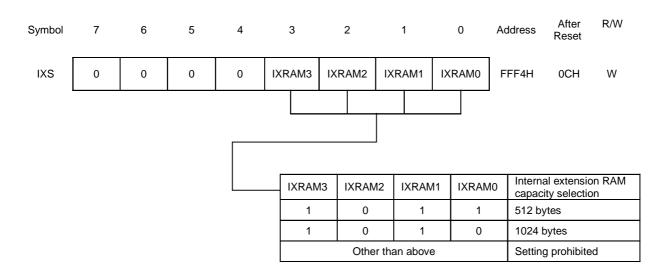

| 21.2 Internal Extension RAM Size Switching Register | 344 |

| 21.3 Flash memory programming                       | 345 |

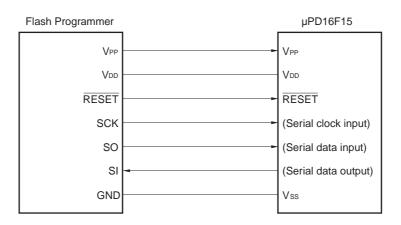

| 21.3.1 Selection of transmission method             | 345 |

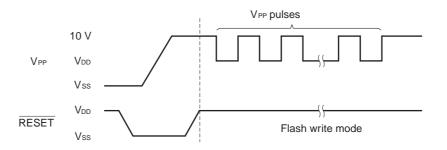

| 21.3.2 Initialization of the programming mode       | 345 |

| 21.3.3 Flash memory programming function            | 346 |

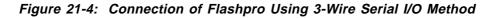

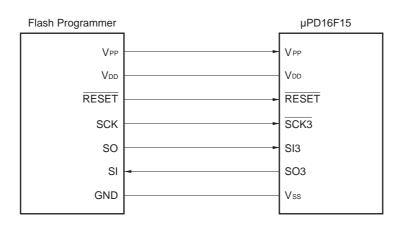

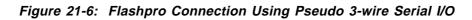

| 21.3.4 Flashpro connection                          | 346 |

| 21.3.5 Flash programming precautions                | 347 |

| Chapter 22 Instruction Set 3                       | \$49 |

|----------------------------------------------------|------|

| 22.1 Legends Used in Operation List                | 350  |

| 22.1.1 Operand identifiers and description methods | 350  |

| 22.1.2 Description of "operation" column           | 351  |

| 22.1.3 Description of "flag operation" column      | 351  |

| 22.2 Operation List                                | 352  |

| 22.3 Instructions Listed by Addressing Type        | 360  |

##

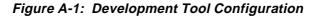

| A.1 Language Processing Software                    | 366 |

|-----------------------------------------------------|-----|

| A.2 Flash Memory Writing Tools                      | 367 |

| A.3 Debugging Tools                                 | 367 |

| A.3.1 Hardware                                      | 367 |

| A.3.2 Software (1/2)                                | 368 |

| A.3.2 Software (2/2)                                | 369 |

| A.4 OS for IBM PC                                   | 370 |

| A.5 Development Environment when Using IE-78001-R-A | 371 |

##

| <b>B.1</b> | Real-Time OS (1/2)                         | 374 |

|------------|--------------------------------------------|-----|

| B.1        | Real-Time OS (2/2)                         | 375 |

| <b>B.2</b> | Fuzzy Inference Development Support System | 376 |

##

| C.1 | Register Index (In Alphabetical Order with Respect to Register Names)  | 378 |

|-----|------------------------------------------------------------------------|-----|

| C.2 | Register Index (In Alphabetical Order with Respect to Register Symbol) | 381 |

| Appendix D Revision History | / 385 |

|-----------------------------|-------|

|-----------------------------|-------|

## **Contents of Figures**

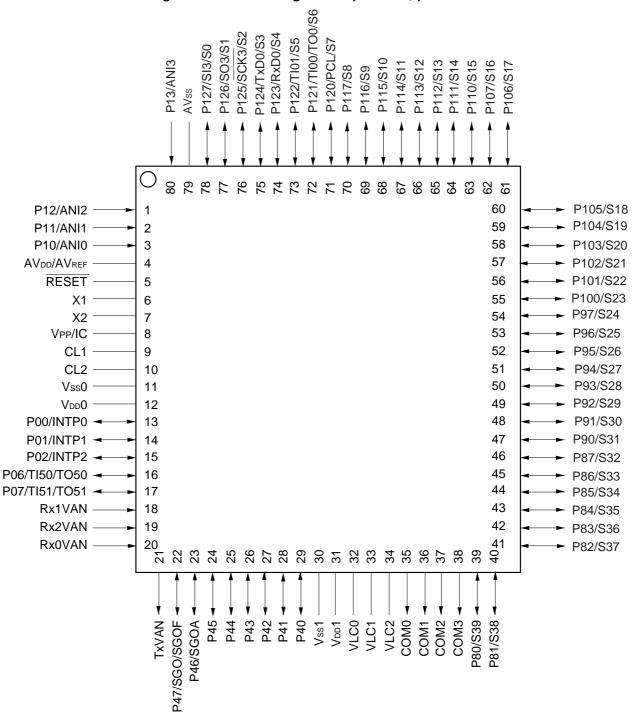

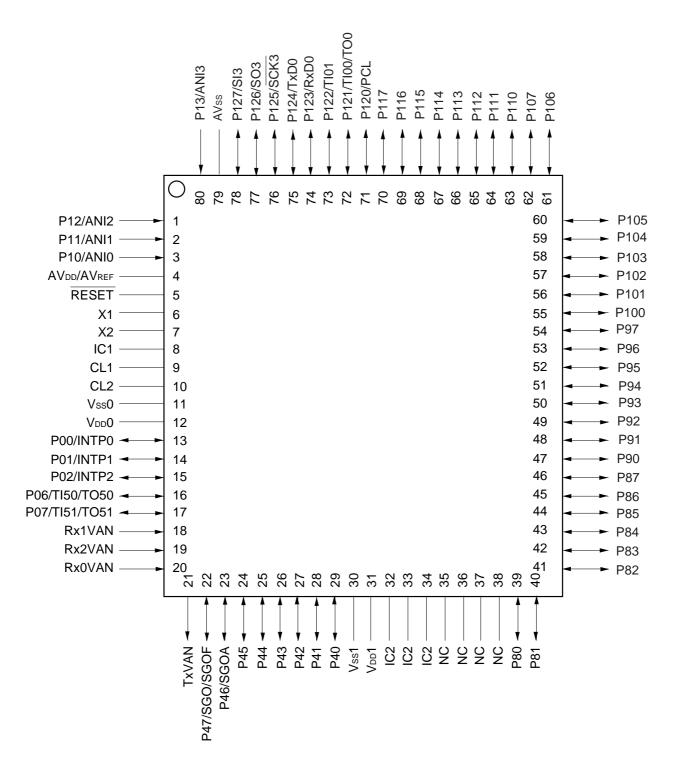

| 1-1  | Pin Configuration μPD1615, μPD16F15         | 27 |

|------|---------------------------------------------|----|

| 1-2  | Pin Configuration μPD1616                   | 28 |

| 1-3  | Block Diagram μPD1615, μPD16F15             | 31 |

| 1-4  | Block Diagram µPD1616                       | 32 |

|      |                                             |    |

| 2-1  | Connection of IC Pins                       | 43 |

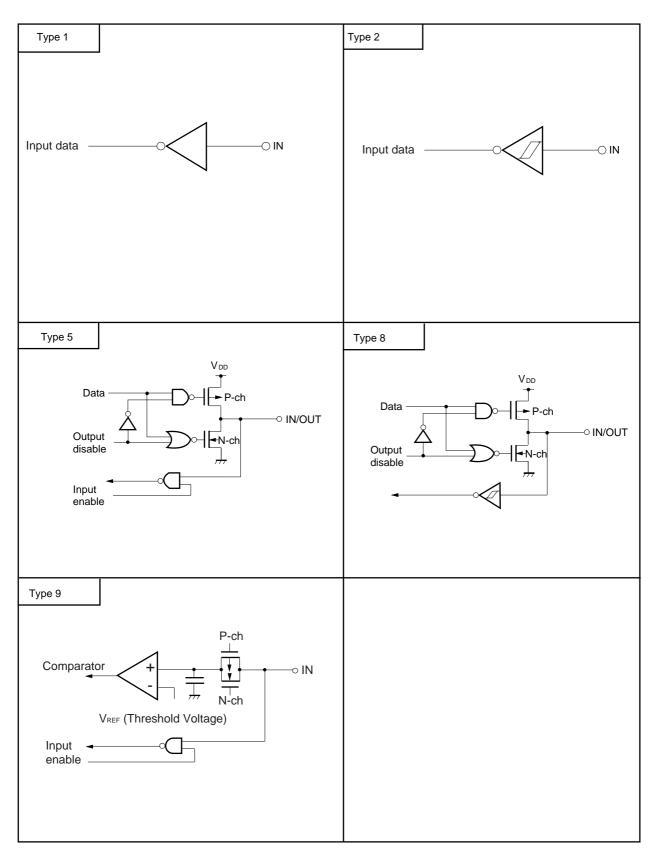

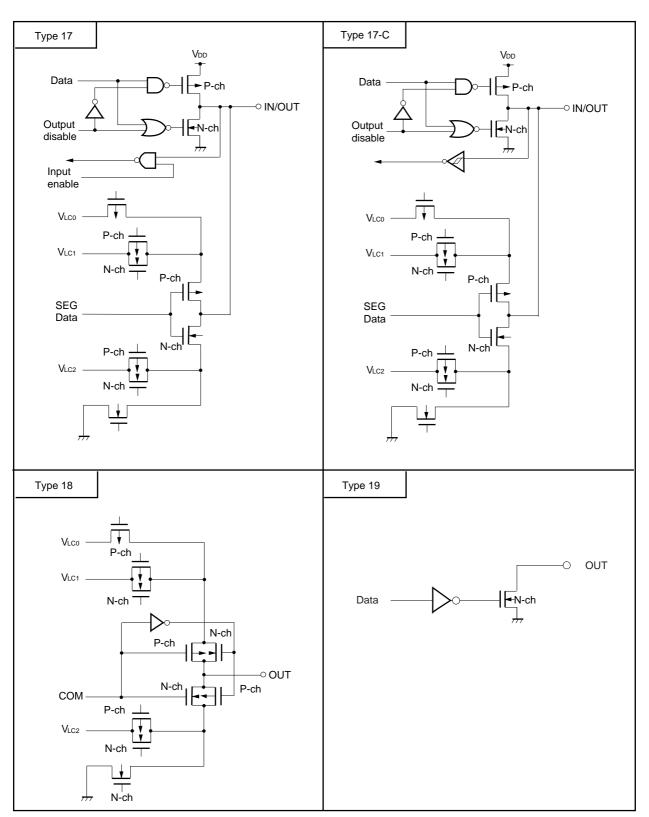

| 2-2  | Pin Input/Output Circuits                   | 48 |

|      |                                             | _  |

| 3-1  | Memory Мар (µPD1615, µPD1616)               | 51 |

| 3-2  | Memory Map (μPD16F15)                       | 52 |

| 3-3  | Data Memory Addressing (µPD1615, µPD1616)   | 56 |

| 3-4  | Data Memory Addressing (µPD16F15)           | 57 |

| 3-5  | Program Counter Configuration               | 58 |

| 3-6  | Program Status Word Configuration           | 58 |

| 3-7  | Stack Pointer Configuration                 | 60 |

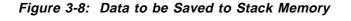

| 3-8  | Data to be Saved to Stack Memory            | 60 |

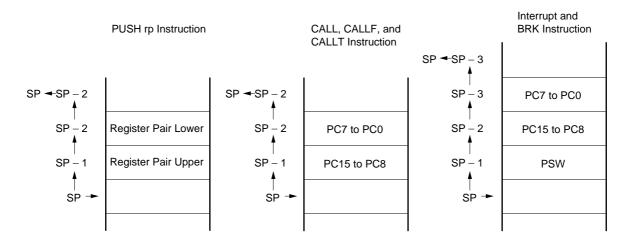

| 3-9  | Data to be Reset to Stack Memory            | 60 |

| 3-10 | General Register Configuration              | 61 |

| 3-11 | Relative Addressing                         | 65 |

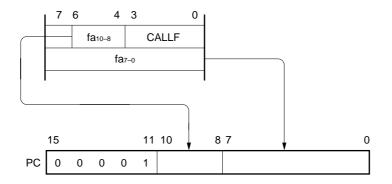

| 3-12 | Immediate Addressing                        | 66 |

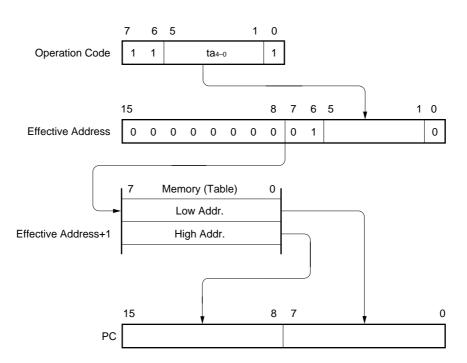

| 3-13 | Table Indirect Addressing                   | 67 |

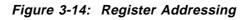

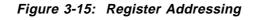

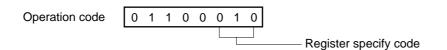

| 3-14 | Register Addressing                         | 68 |

| 3-15 | Register Addressing                         | 70 |

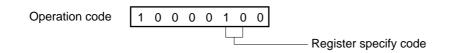

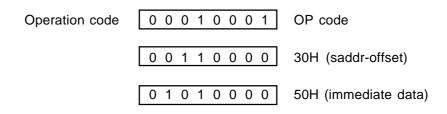

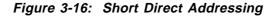

| 3-16 | Short Direct Addressing                     | 72 |

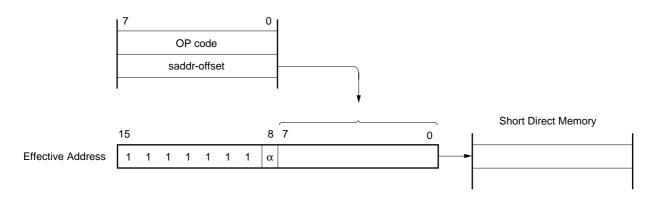

| 3-17 | Special-Function Register (SFR) Addressing  | 73 |

| 3-18 | Special-Function Register (SFR) Addressing  | 74 |

|      |                                             |    |

| 4-1  | Port Types                                  | 78 |

| 4-2  | P00 to P02 and P06, P07 Configurations      | 82 |

| 4-3  | P10 to P13 Configurations                   | 83 |

| 4-4  | P40 to P47 Configurations                   | 84 |

| 4-5  | P80 to P87 Configurations                   | 85 |

| 4-6  | P90 to P97 Configurations                   | 86 |

| 4-7  | P100 to P107 Configurations                 | 87 |

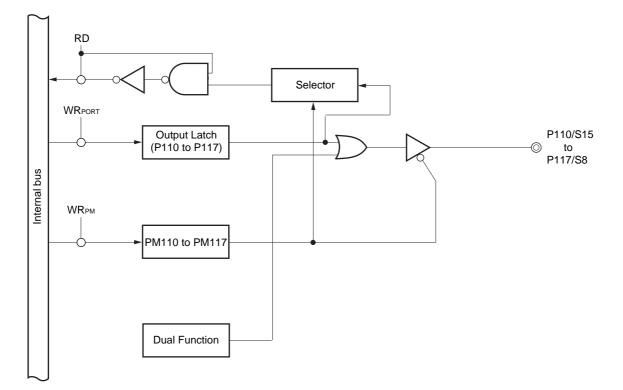

| 4-8  | P110 to P117 Configurations                 | 88 |

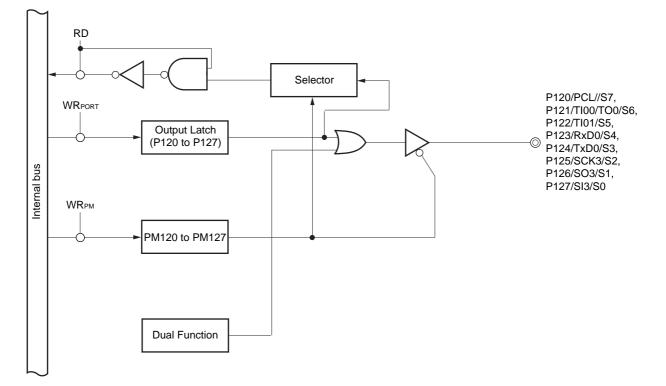

| 4-9  | P120 to P127 Configurations                 | 89 |

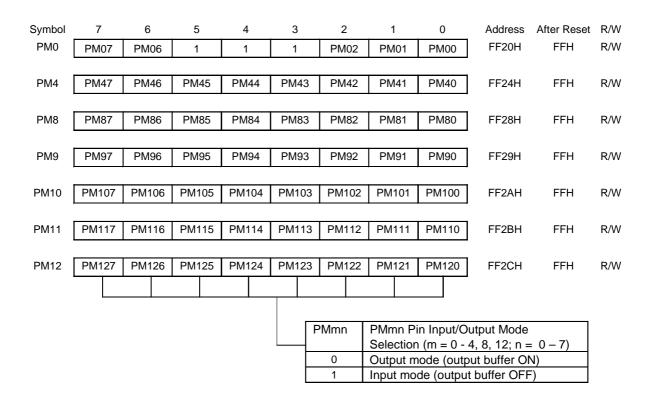

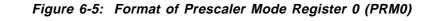

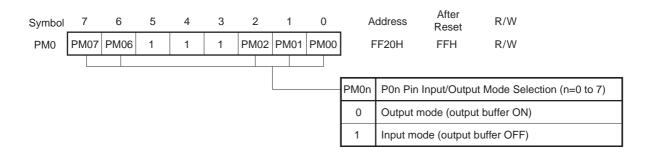

| 4-10 | Port Mode Register Format                   | 91 |

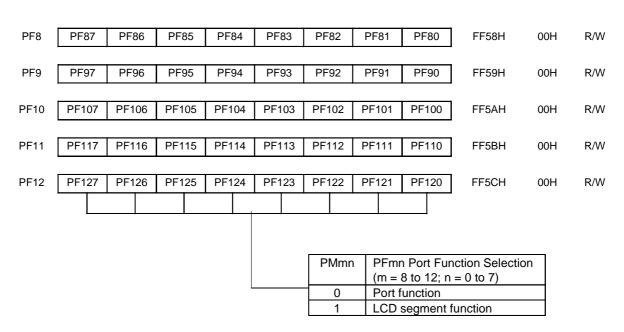

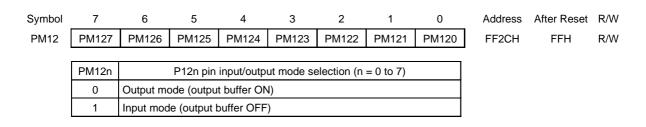

| 4-11 | Port Function Register (PF8 to PF12) Format | 92 |

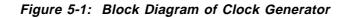

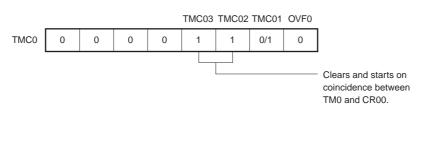

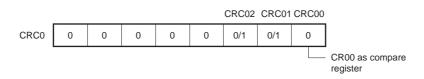

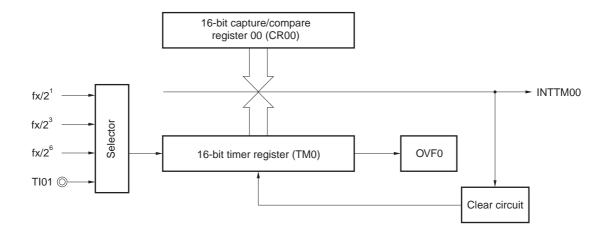

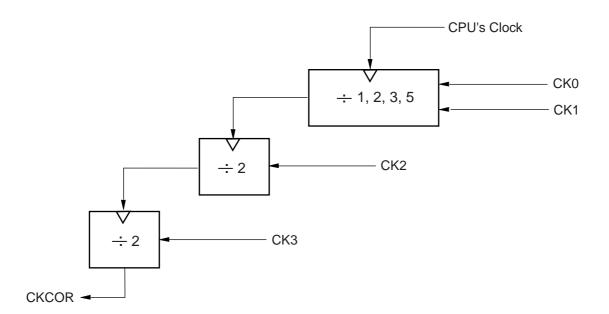

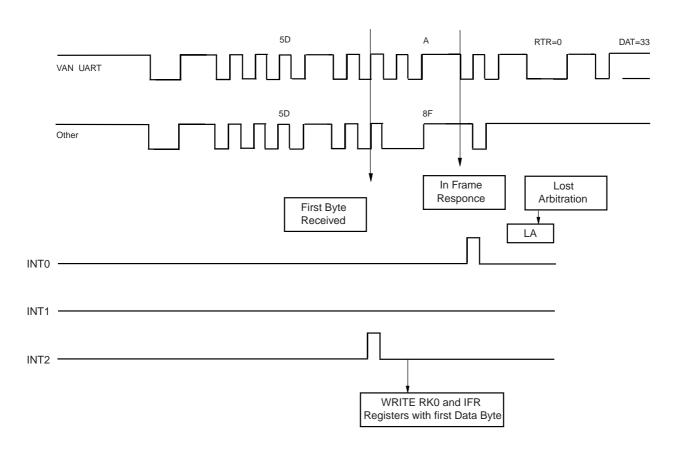

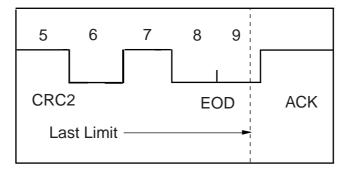

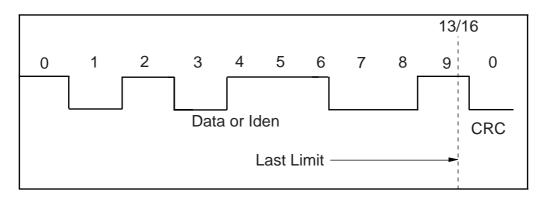

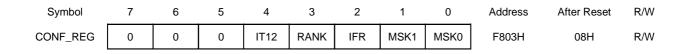

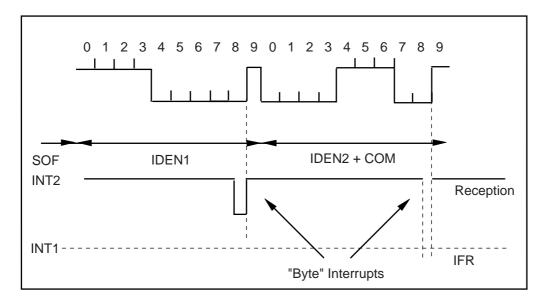

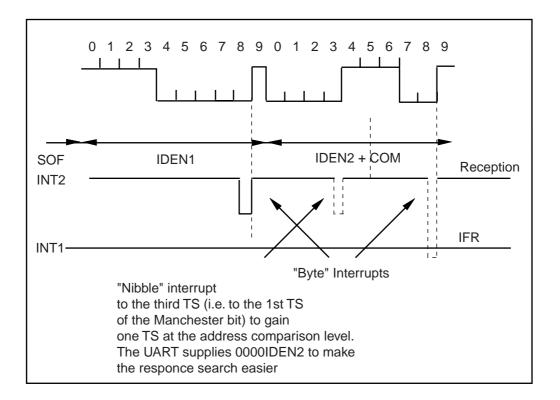

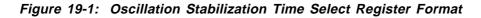

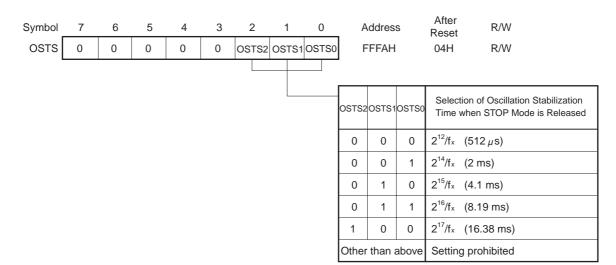

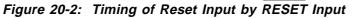

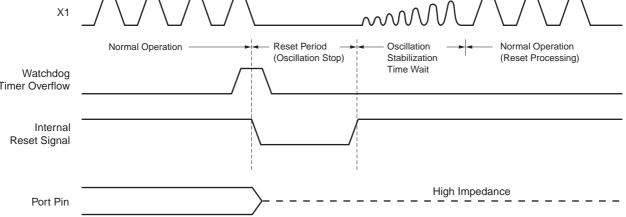

|      | ,                                           |    |